Power over Ethernet

IEEE 802.3af PD Interface with

Integrated Switching Regulator

# **FEATURES**

- Complete Power Interface Port for IEEE 802<sup>®</sup>.3af Powered Device (PD)

- Onboard 100V, 400mA UVLO Switch

- Precision Dual Level Inrush Current Limit

- Integrated Current Mode Switching Regulator

- Onboard 25kΩ Signature Resistor with Disable

- Programmable Classification Current (Class 0-4)

- Thermal Overload Protection

- Power Good Signal

- Integrated Error Amplifier and Voltage Reference

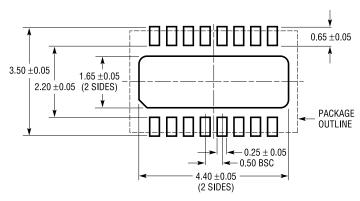

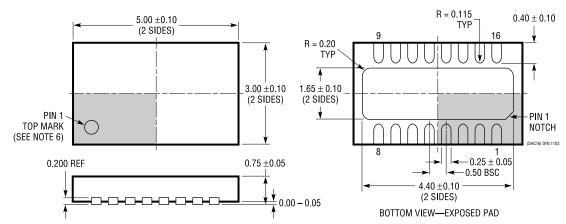

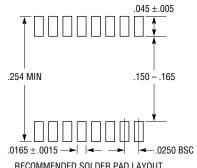

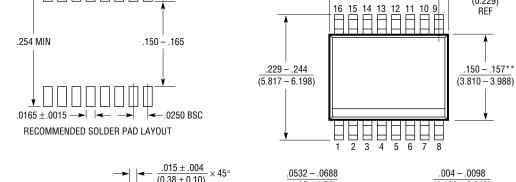

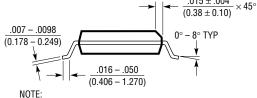

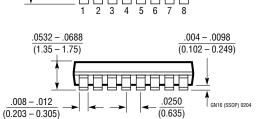

- Low Profile 16-Pin SSOP and 3mm × 5mm DFN Packages

# **APPLICATIONS**

- IP Phone Power Management

- Wireless Access Points

- Security Cameras

- Power over Ethernet

T, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

# DESCRIPTION

The LTC®4267 combines an IEEE 802.3af compliant Powered Device (PD) interface with a current mode switching regulator, providing a complete power solution for PD applications. The LTC4267 integrates the  $25 k\Omega$  signature resistor, classification current source, thermal overload protection, signature disable and power good signal along with an undervoltage lockout optimized for use with the IEEE-required diode bridge. The precision dual level input current limit allows the LTC4267 to charge large load capacitors and interface with legacy PoE systems.

The current mode switching regulator is designed for driving a 6V rated N-channel MOSFET and features programmable slope compensation, soft-start, and constant frequency operation, minimizing noise even with light loads. The LTC4267 includes an onboard error amplifier and voltage reference allowing use in both isolated and nonisolated configurations.

The LTC4267 is available in space saving, low profile 16-pin SSOP or DFN packages.

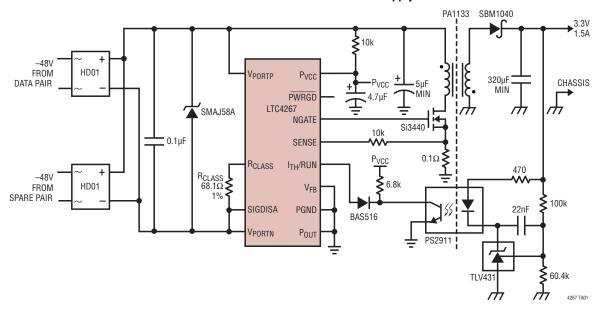

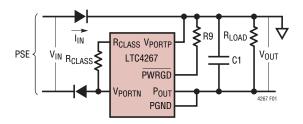

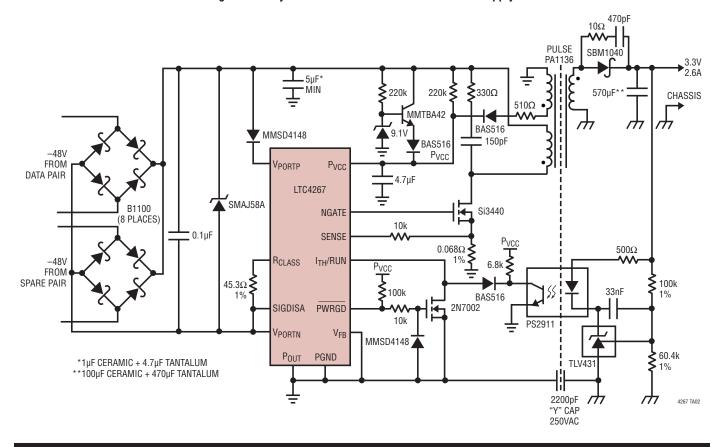

# TYPICAL APPLICATION

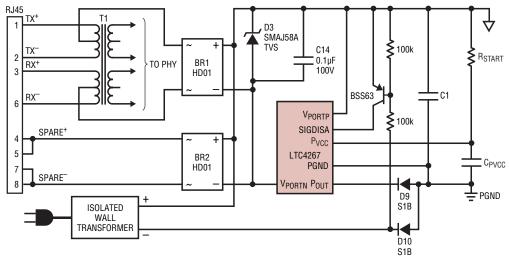

#### Class 2 PD with 3.3V Isolated Power Supply

# **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| 0.3V to -100V             |

|---------------------------|

| V <sub>PORTN</sub> -0.3V  |

|                           |

| 0.3V to 8V                |

| 5mA into P <sub>VCC</sub> |

| $V_{PORTN} - 0.3V$        |

| 10mA                      |

| 100mA                     |

| $0.3V$ to $P_{VCC}$       |

| 0.3V to 3.5V              |

|                           |

| SENSE to PGND Voltage                | -0.3V to 1V |

|--------------------------------------|-------------|

| NGATE Peak Output Current (<10µs)    | 1A          |

| Operating Ambient Temperature Range  |             |

| LTC4267C                             | 0°C to 70°C |

| LTC4267I4                            | 0°C to 85°C |

| Junction Temperature                 |             |

| GN Package                           | 150°C       |

| DHC Package                          | 125°C       |

| Storage Temperature Range65          | °C to 150°C |

| Lead Temperature (Soldering, 10 sec) | 300°C       |

# PACKAGE/ORDER INFORMATION

Lead Free Tape and Reel: Add #TRPBF Lead Free Part Marking: http://www.linear.com/leadfree/

| PGND   2                                               | I <sub>TH</sub> /RUN       | TOP VIEW                                                                         | 1 <u>16</u> V <sub>FB</sub>                    | ORDER PART<br>NUMBER | PGND 1                       | VIEW 16 PGND                      | ORDER PART<br>NUMBER |

|--------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------|------------------------------------------------|----------------------|------------------------------|-----------------------------------|----------------------|

| NC 6                                                   | P <sub>VCC</sub>           | 4  <br>4  <br>==   17                                                            | 113 V <sub>PORTP</sub>                         |                      | NGATE 3                      | 14 SENSE<br>13 V <sub>PORTP</sub> |                      |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | NC<br>V <sub>PORTN</sub>   | 6  <br>7  <br>7                                                                  | 1 <u>10</u> P <sub>OUT</sub>                   |                      | NC 6<br>V <sub>PORTN</sub> 7 | 11 PWRGD<br>10 P <sub>OUT</sub>   |                      |

| TO ELECTRICALLY ISOLATED FOR HEAT STINK                | T <sub>JI</sub><br>EXPOSED | AD (3mm × 5mm)<br><sub>MAX</sub> = 125°C, θ <sub>JA</sub> =<br>) PAD (PIN 17) MU | ) PLASTIC DFN<br>= 43.5°C/W<br>JST BE SOLDERED |                      | 16-LEAD NARRO                | W PLASTIC SSOP                    |                      |

$Consult\ LTC\ Marketing\ for\ parts\ specified\ with\ wider\ operating\ temperature\ ranges.\ {}^*The\ temperature\ grades\ are\ identified\ by\ a\ label\ on\ the\ shipping\ container.$

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                | PARAMETER                                | CONDITIONS                                                                        |   | MIN   | TYP   | MAX   | UNITS |

|-----------------------|------------------------------------------|-----------------------------------------------------------------------------------|---|-------|-------|-------|-------|

| V <sub>PORTN</sub>    | Supply Voltage                           | Voltage with Respect to V <sub>PORTP</sub> Pin                                    |   |       |       |       |       |

|                       | Maximum Operating Voltage                | (Notes 4, 5, 6)                                                                   | • |       |       | -57   | V     |

|                       | Signature Range                          | , ,                                                                               | • | -1.5  |       | -9.5  | V     |

|                       | Classification Range                     |                                                                                   | • | -12.5 |       | -21   | V     |

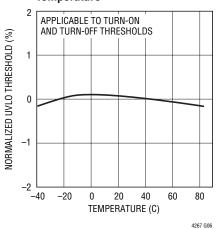

|                       | UVLO Turn-On Voltage                     |                                                                                   | • | -34.8 | -36.0 | -37.2 | V     |

|                       | UVLO Turn-Off Voltage                    |                                                                                   | • | -29.3 | -30.5 | -31.5 | V     |

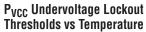

| V <sub>TURNON</sub>   | P <sub>VCC</sub> Turn-On Voltage         | Voltage with Respect to PGND                                                      | • | 7.8   | 8.7   | 9.2   | V     |

| V <sub>TURNOFF</sub>  | P <sub>VCC</sub> Turn-Off Voltage        | Voltage with Respect to PGND                                                      | • | 4.6   | 5.7   | 6.8   | V     |

| V <sub>HYST</sub>     | P <sub>VCC</sub> Hysteresis              | V <sub>TURNON</sub> – V <sub>TURNOFF</sub>                                        | • | 1.5   | 3.0   |       | V     |

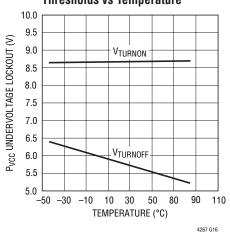

| V <sub>CLAMP1mA</sub> | P <sub>VCC</sub> Shunt Regulator Voltage | I <sub>PVCC</sub> = 1mA, V <sub>ITH</sub> /RUN = 0V, Voltage with Respect to PGND | • | 8.3   | 9.4   | 10.3  | V     |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                                       | PARAMETER                                                       | CONDITIONS                                                                                                                                                                    |     | MIN        | TYP        | MAX        | UNITS          |

|----------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------------|------------|----------------|

| V <sub>MARGIN</sub>                          | V <sub>CLAMP1mA</sub> – V <sub>TURNON</sub> Margin              |                                                                                                                                                                               | •   | 0.05       | 0.6        |            | V              |

| I <sub>VPORTN_ON</sub>                       | V <sub>PORTN</sub> Supply Current when ON                       | $V_{PORTN} = -48V$ , $P_{OUT}$ , $\overline{PWRGD}$ , SIGDISA Floating                                                                                                        | •   |            |            | 3          | mA             |

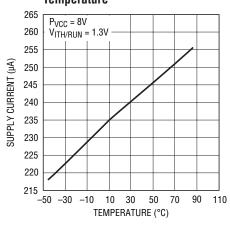

| I <sub>PVCC_ON</sub>                         | P <sub>VCC</sub> Supply Current<br>Normal Operation<br>Start-Up | (Note 7)<br>V <sub>ITH</sub> /RUN – PGND = 1.3V<br>P <sub>VCC</sub> – PGND = V <sub>TURNON</sub> – 100mV                                                                      | •   |            | 240<br>40  | 350<br>90  | μA<br>μA       |

| IVPORTN_CLASS                                | V <sub>PORTN</sub> Supply Current<br>During Classification      | V <sub>PORTN</sub> = -17.5V, P <sub>OUT</sub> Tied to V <sub>PORTP</sub> , R <sub>CLASS</sub> , SIGDISA Floating (Note 8)                                                     | •   | 0.35       | 0.5        | 0.65       | mA             |

| ΔI <sub>CLASS</sub>                          | Current Accuracy<br>During Classification                       | $10mA < I_{CLASS} < 40mA, -12.5V \le V_{PORTN} \le -21V$ (Notes 9, 10)                                                                                                        | •   |            |            | ±3.5       | %              |

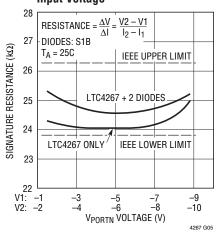

| R <sub>SIGNATURE</sub>                       | Signature Resistance                                            | $-1.5V \le V_{PORTN} \le -9.5V$ , $P_{OUT}$ Tied to $V_{PORTP}$ , IEEE 802.3af 2-Point Measurement (Notes 4, 5)                                                               | •   | 23.25      |            | 26.00      | kΩ             |

| R <sub>INVALID</sub>                         | Invalid Signature Resistance                                    | $-1.5V \le V_{PORTN} \le -9.5V$ , SIGDISA and $P_{OUT}$ Tied to $V_{PORTP}$ , IEEE 802.3af 2-Point Measurement (Notes 4, 5)                                                   | •   |            | 9          | 11.8       | kΩ             |

| V <sub>IH</sub>                              | Signature Disable<br>High Level Input Voltage                   | With Respect to V <sub>PORTN</sub><br>High Level Invalidates Signature (Note 11)                                                                                              | •   | 3          |            | 57         | V              |

| $V_{IL}$                                     | Signature Disable<br>Low Level Input Voltage                    | With Respect to V <sub>PORTN</sub> Low Level Enables Signature                                                                                                                | •   |            |            | 0.45       | V              |

| R <sub>INPUT</sub>                           | Signature Disable, Input Resistance                             | With Respect to V <sub>PORTN</sub>                                                                                                                                            | •   | 100        |            |            | kΩ             |

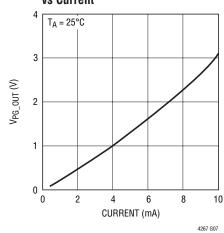

| V <sub>PG_OUT</sub>                          | Power Good Output Low Voltage                                   | I = 1mA V <sub>PORTN</sub> = -48V,<br>PWRGD Referenced to V <sub>PORTN</sub>                                                                                                  | •   |            |            | 0.5        | V              |

| V <sub>PG_FALL</sub><br>V <sub>PG_RISE</sub> | Power Good Trip Point                                           | V <sub>PORTN</sub> = -48V, Voltage between V <sub>PORTN</sub> and P <sub>OUT</sub> (Note 10) P <sub>OUT</sub> Falling P <sub>OUT</sub> Rising                                 | • • | 1.3<br>2.7 | 1.5<br>3.0 | 1.7<br>3.3 | V              |

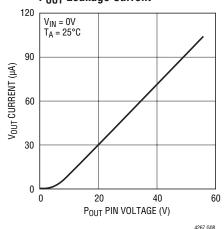

| I <sub>PG_LEAK</sub>                         | Power Good Leakage Current                                      | V <sub>PORTN</sub> = 0V, PWRGD FET Off, V <sub>PWRGD</sub> = 57V                                                                                                              | •   |            |            | 1          | μА             |

| R <sub>ON</sub>                              | On-Resistance                                                   | I = 300mA, V <sub>PORTN</sub> = -48V, Measured from V <sub>PORTN</sub> to P <sub>OUT</sub> (Note 10)                                                                          | •   |            | 1.0        | 1.6<br>2   | $\Omega$       |

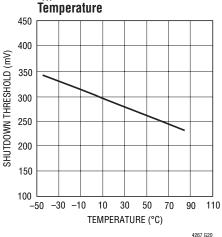

| V <sub>ITHSHDN</sub>                         | Shutdown Threshold (at I <sub>TH</sub> /RUN)                    | $P_{VCC} - PGND = V_{TURNON} + 100mV$                                                                                                                                         | •   | 0.15       | 0.28       | 0.45       | V              |

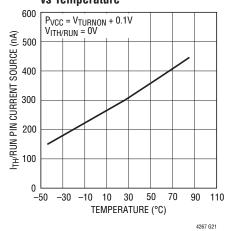

| I <sub>THSTART</sub>                         | Start-Up Current Source at I <sub>TH</sub> /RUN                 | V <sub>ITH</sub> /RUN - PGND = 0V, P <sub>VCC</sub> - P <sub>GND</sub> = 8V                                                                                                   |     | 0.2        | 0.3        | 0.4        | μА             |

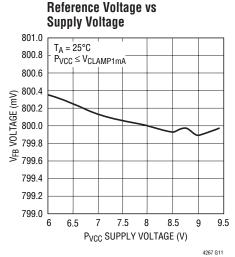

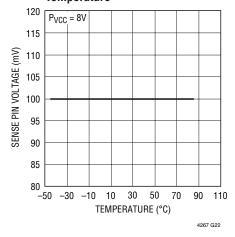

| $V_{FB}$                                     | Regulated Feedback Voltage                                      | Referenced to PGND, P <sub>VCC</sub> – P <sub>GND</sub> = 8V (Note 12)                                                                                                        | •   | 0.780      | 0.800      | 0.812      | V              |

| I <sub>FB</sub>                              | V <sub>FB</sub> Input Current                                   | P <sub>VCC</sub> – P <sub>GND</sub> = 8V (Note 12)                                                                                                                            |     |            | 10         | 50         | nA             |

| g <sub>m</sub>                               | Error Amplifier Transconductance                                | I <sub>TH</sub> /RUN Pin Load = ±5μA (Note 12)                                                                                                                                |     | 200        | 333        | 500        | μA/V           |

| $\Delta V_{O(LINE)}$                         | Output Voltage Line Regulation                                  | V <sub>TURNOFF</sub> < P <sub>VCC</sub> < V <sub>CLAMP</sub> (Note 12)                                                                                                        |     |            | 0.05       |            | mV/V           |

| $\Delta V_{O(LOAD)}$                         | Output Voltage Load Regulation                                  | I <sub>TH</sub> /RUN Sinking 5μA, P <sub>VCC</sub> – P <sub>GND</sub> = 8V (Note 12)<br>I <sub>TH</sub> /RUN Sourcing 5μA, P <sub>VCC</sub> – P <sub>GND</sub> = 8V (Note 12) |     |            | 3<br>3     |            | mV/μA<br>mV/μA |

| I <sub>POUT_LEAK</sub>                       | P <sub>OUT</sub> Leakage                                        | V <sub>PORTN</sub> = 0V, Power MOSFET Off,<br>P <sub>OUT</sub> = 57V (Note 13)                                                                                                | •   |            |            | 150        | μА             |

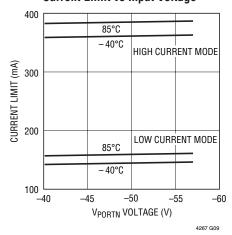

| I <sub>LIM_HI</sub>                          | Input Current Limit, High Level                                 | $V_{PORTN} = -48V$ , $P_{OUT} = -43V$ (Note 14, 15)<br>$0^{\circ}C \le T_{A} \le 70^{\circ}C$<br>$-40^{\circ}C \le T_{A} \le 85^{\circ}C$                                     | • • | 325<br>300 | 375<br>375 | 400<br>400 | mA<br>mA       |

| I <sub>LIM_L0</sub>                          | Input Current Limit, Low Level                                  | V <sub>PORTN</sub> = -48V, P <sub>OUT</sub> = -43V (Note 14, 15)                                                                                                              | •   | 80         | 140        | 180        | mA             |

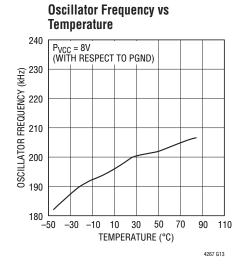

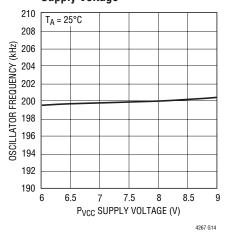

| f <sub>OSC</sub>                             | Oscillator Frequency                                            | V <sub>ITH</sub> /RUN – PGND = 1.3V, P <sub>VCC</sub> – P <sub>GND</sub> = 8V                                                                                                 |     | 180        | 200        | 240        | kHz            |

| DC <sub>ON(MIN)</sub>                        | Minimum Switch On Duty Cycle                                    | V <sub>ITH</sub> /RUN – PGND = 1.3V, V <sub>FB</sub> – PGND = 0.8V,<br>P <sub>V</sub> CC – P <sub>GND</sub> = 8V                                                              |     |            | 6          | 8          | %              |

| DC <sub>ON(MAX)</sub>                        | Maximum Switch On Duty Cycle                                    | V <sub>ITH</sub> /RUN – PGND = 1.3V, V <sub>FB</sub> – PGND = 0.8V,<br>P <sub>VCC</sub> – P <sub>GND</sub> = 8V                                                               |     | 70         | 80         | 90         | %              |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                | PARAMETER                              | CONDITIONS                                                           |     | MIN | TYP | MAX | UNITS |

|-----------------------|----------------------------------------|----------------------------------------------------------------------|-----|-----|-----|-----|-------|

| t <sub>RISE</sub>     | NGATE Drive Rise Time                  | C <sub>LOAD</sub> = 3000pF, P <sub>VCC</sub> - P <sub>GND</sub> = 8V |     |     | 40  |     | ns    |

| t <sub>FALL</sub>     | NGATE Drive Fall Time                  | C <sub>LOAD</sub> = 3000pF, P <sub>VCC</sub> - P <sub>GND</sub> = 8V |     |     | 40  |     | ns    |

| V <sub>IMAX</sub>     | Peak Current Sense Voltage             | $R_{SL} = 0$ , $P_{VCC} - P_{GND} = 8V$ (Note 16)                    | •   | 90  | 100 | 115 | mV    |

| I <sub>SLMAX</sub>    | Peak Slope Compensation Output Current | P <sub>VCC</sub> - P <sub>GND</sub> = 8V (Note 17)                   | 5   |     | μА  |     |       |

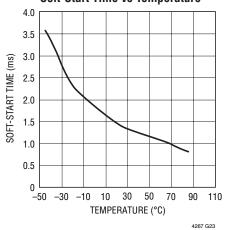

| t <sub>SFST</sub>     | Soft-Start Time                        | P <sub>VCC</sub> - P <sub>GND</sub> = 8V                             | 1.4 |     | ms  |     |       |

| T <sub>SHUTDOWN</sub> | Thermal Shutdown Trip Temperature      | (Notes 14, 18)                                                       |     | 140 |     | °C  |       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2:  $P_{VCC}$  internal clamp circuit self regulates to 9.4V with respect to PGND.

**Note 3:** The LTC4267 operates with a negative supply voltage in the range of -1.5V to -57V. To avoid confusion, voltages for the PD interface are always referred to in terms of absolute magnitude. Terms such as "maximum negative voltage" refer to the largest negative voltage and a "rising negative voltage" refers to a voltage that is becoming more negative.

**Note 4:** The LTC4267 is designed to work with two polarity protection diode drops between the PSE and PD. Parameter ranges specified in the Electrical Characteristics section are with respect to this product pins and are designed to meet IEEE 802.3af specifications when these diode drops are included. See the Application Information section.

**Note 5:** Signature resistance is measured via the two-point  $\Delta V/\Delta I$  method as defined by IEEE 802.3af. The PD signature resistance is offset from the  $25k\Omega$  to account for diode resistance. With two series diodes, the total PD resistance will be between  $23.75k\Omega$  and  $26.25k\Omega$  and meet IEEE 802.3af specifications. The minimum probe voltages measured at the LTC4267 pins are -1.5V and -2.5V. The maximum probe voltages are -8.5V and -9.5V.

**Note 6:** The PD interface includes hysteresis in the UVLO voltages to preclude any start-up oscillation. Per IEEE 802.3af requirements, the PD will power up from a voltage source with  $20\Omega$  series resistance on the first trial.

**Note 7:** Dynamic Supply current is higher due to the gate charge being delivered at the switching frequency.

**Note 8:** I<sub>VPORTN\_CLASS</sub> does not include classification current programmed at the R<sub>CLASS</sub> pin. Total current in classification mode will be I<sub>VPORTN\_CLASS</sub> + I<sub>CLASS</sub> (See note 9).

**Note 9:**  $I_{CLASS}$  is the measured current flowing through  $R_{CLASS}$ .  $\Delta I_{CLASS}$  accuracy is with respect to the ideal current defined as  $I_{CLASS} = 1.237$ /

$R_{\text{CLASS}}.$  The current accuracy does not include variations in  $R_{\text{CLASS}}$  resistance. The total classification current for a PD also includes the IC quiescent current ( $I_{\text{VPORTN\_CLASS}}$ ). See Applications Information.

**Note 10:** For the DHC package, this parameter is assured by design and wafer level testing.

**Note 11:** To disable the  $25k\Omega$  signature, tie SIGDISA to  $V_{PORTP}$  or hold SIGDISA high with respect to  $V_{PORTN}$ . See Applications Information.

**Note 12:** The switching regulator is tested in a feedback loop that servos  $V_{FB}$  to the output of the error amplifier while maintaining  $I_{TH}/RUN$  at the midpoint of the current limit range.

**Note 13:**  $I_{POUT\_LEAK}$  includes current drawn through  $P_{OUT}$  by the power good status circuit. This current is compensated for in the  $25k\Omega$  signature resistance and does not affect PD operation.

**Note 14:** The LTC4267 PD Interface includes thermal protection. In the event of an overtemperature condition, the PD interface will turn off the switching regulator until the part cools below the overtemperature limit. The LTC4267 is also protected against thermal damage from incorrect classification probing by the PSE. If the LTC4267 exceeds the overtemperature threshold, the classification load current is disabled.

**Note 15:** The PD interface includes dual level input current limit. At turnon, before the  $P_{OUT}$  load capacitor is charged, the PD current level is set to a low level. After the load capacitor is charged and the  $P_{OUT} - V_{PORTN}$  voltage difference is below the power good threshold, the PD switches to high level current limit. The PD stays in high level current limit until the input voltage drops below the UVLO turn-off threshold.

**Note 16:** Peak current sense voltage is reduced dependent on duty cycle and an optional external resistor in series with the SENSE pin ( $R_{SL}$ ). For details, refer to the programmable slope compensation feature in the Applications Information section.

Note 17: Guaranteed by design.

**Note 18:** The PD interface includes overtemperature protection that is intended to protect the device from momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

LINEAD

# TYPICAL PERFORMANCE CHARACTERISTICS

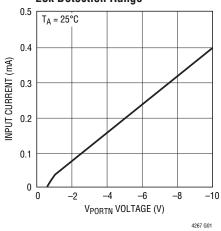

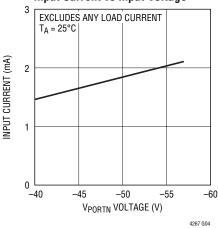

#### Input Current vs Input Voltage 25k Detection Range

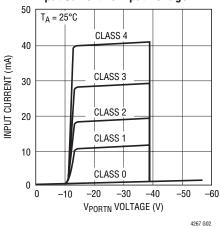

#### Input Current vs Input Voltage

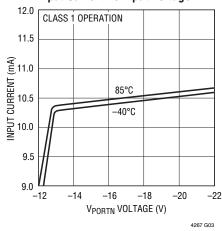

Input Current vs Input Voltage

#### **Input Current vs Input Voltage**

#### Signature Resistance vs Input Voltage

#### Normalized UVLO Threshold vs Temperature

# Power Good Output Low Voltage vs Current

# P<sub>OUT</sub> Leakage Current

#### **Current Limit vs Input Voltage**

788

\_50

-30 -10

# TYPICAL PERFORMANCE CHARACTERISTICS

4267 G10

# Reference Voltage vs Temperature 812 Pvcc = 8V 808 (Au) 39V A 796 792

#### Oscillator Frequency vs Supply Voltage

10 30 50 70 90 110

TEMPERATURE (°C)

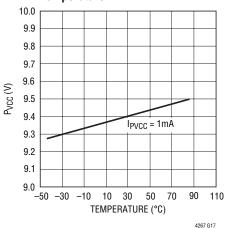

P<sub>VCC</sub> Shunt Regulator Voltage vs Temperature

I<sub>PVCC</sub> Supply Current vs Temperature

# TYPICAL PERFORMANCE CHARACTERISTICS

TEMPERATURE (°C)

Start-Up I<sub>PVCC</sub> Supply Current vs

START-UP SUPPLY CURRENT (µA) 50 40 30 20 10 -50 -30 -10 10 30 50 70 90 110

#### I<sub>TH</sub>/RUN Shutdown Threshold vs **Temperature**

# $I_{TH}/RUN$ Start-Up Current Source vs Temperature

#### **Peak Current Sense Voltage vs** Temperature

# **Soft-Start Time vs Temperature**

# PIN FUNCTIONS (GN/DHC)

I<sub>TH</sub>/RUN (Pin 2/Pin 1): Current Threshold/Run Input. This pin performs two functions. It serves as the switching regulator error amplifier compensation point as well as the run/shutdown control input. Nominal voltage range is 0.7V to 1.9V. Forcing the pin below 0.28V with respect to PGND causes the controller to shut down.

**PGND** (**Pin 1, 8, 9, 16/Pin 2, 15**): Switching Regulator Negative Supply. This pin is the negative supply rail for the switching regulator controller and must be tied to P<sub>OUT</sub>.

**NGATE (Pin 3/Pin 3):** Gate Driver Output. This pin drives the regulator's external N-Channel MOSFET and swings from PGND to P<sub>VCG</sub>.

**P**<sub>VCC</sub> (**Pin 4/Pin 4**): Switching Regulator Positive Supply. This pin is the positive supply rail for the switching regulator and must be closely decoupled to PGND.

$R_{CLASS}$  (Pin 5/Pin 5): Class Select Input. Used to set the current value the PD maintains during classification. Connect a resistor between  $R_{CLASS}$  and  $V_{PORTN}$  (see Table 2).

**V<sub>PORTN</sub>** (**Pin 7/Pin 7**): Negative Power Input. Tie to the –48V input port through the input diodes.

**P<sub>OUT</sub>** (**Pin 10/Pin 10**): Power Output. Supplies -48V to the switching regulator PGND pin and any additional PD loads through an internal power MOSFET that limits input current. P<sub>OUT</sub> is high impedance until the voltage reaches the turn-on UVLO threshold. The output is then current limited. See the Application Information section.

PWRGD (Pin 11/Pin 11): Power Good Output, Open-Drain. Indicates that the PD MOSFET is on and the switching regulator can start operation. Low impedance indicates power is good. PWRGD is high impedance during detection, classification and in the event of a thermal overload. PWRGD is referenced to VPORTN.

**SIGDISA** (Pin 12/Pin 12): Signature Disable Input. SIGDISA allows the PD to present an invalid signature resistance and remain inactive. Connecting SIGDISA to  $V_{PORTP}$  lowers the signature resistance to an invalid value and disables all functions of the LTC4267. If unused, tie SIGDISA to  $V_{PORTN}$ .

**V**PORTP (Pin 13/Pin 13): Positive Power Input. Tie to the input port power return through the input diodes.

**SENSE (Pin 14/Pin 14):** Current Sense. This pin performs two functions. It monitors the regulator switch current by reading the voltage across an external sense resistor. It also injects a current ramp that develops a slope compensation voltage across an optional external programming resistor. See the Applications Information section.

**V<sub>FB</sub>** (**Pin 15/Pin 16**): Feedback Input. Receives the feedback voltage from the external resistor divider across the output.

NC (Pin 6/Pin 6, 8, 9): No Internal Connection.

**Backside Connection (DHC Only, Pin 17):** Exposed Pad. This exposed pad must be soldered to an electrically isolated and thermally conductive PC board heat sink.

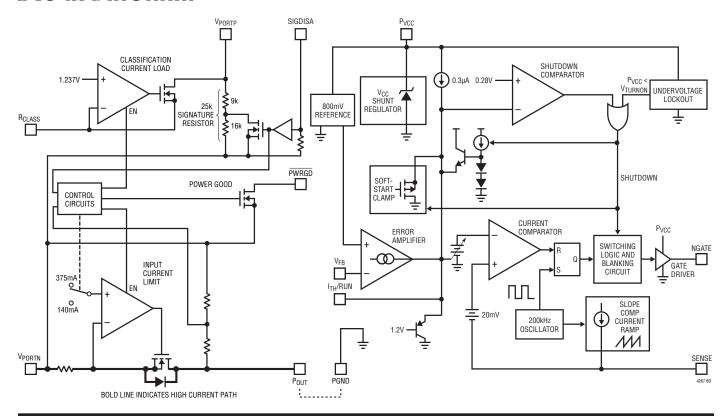

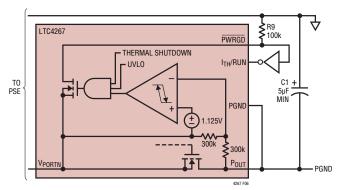

# **BLOCK DIAGRAM**

# APPLICATIONS INFORMATION

#### **OVERVIEW**

The LTC4267 is partitioned into two major blocks: a Powered Device (PD) interface controller and a current mode flyback switching regulator. The Powered Device (PD) interface is intended for use as the front end of a PD adhering to the IEEE 802.3af standard, and includes a trimmed  $25k\Omega$  signature resistor, classification current source, and an input current limit circuit. With these functions integrated into the LTC4267, the signature and power interface for a PD can be built that meets all the requirements of the IEEE 802.3af specification with a minimum of external components.

The switching regulator portion of the LTC4267 is a constant frequency current mode controller that is optimized for Power over Ethernet applications. The regulator is designed to drive a 6V N-channel MOSFET and features soft-start and programmable slope compensation. The integrated error amplifier and precision reference give the PD designer the option of using a nonisolated topology without the need for an external amplifier or reference. The

LTC4267 has been specifically designed to interface with both IEEE compliant Power Sourcing Equipment (PSE) and legacy PSEs which do not meet the inrush current requirement of the IEEE 802.3af specification. By setting the initial inrush current limit to a low level, a PD using the LTC4267 minimizes the current drawn from the PSE during start-up. After powering up, the LTC4267 switches to the high level current limit, thereby allowing the PD to consume up to 12.95W if an IEEE 802.3af PSE is present. This low level current limit also allows the LTC4267 to charge arbitrarily large load capacitors without exceeding the inrush limits of the IEEE 802.3af specification. This dual level current limit provides the system designer with flexibility to design PDs which are compatible with legacy PSEs while also being able to take advantage of the higher power available in an IEEE 802.3af system.

Using an LTC4267 for the power and signature interface functions of a PD provides several advantages. The LTC4267 current limit circuit includes an onboard 100V, 400mA power MOSFET. This low leakage MOSFET is

specified to avoid corrupting the  $25k\Omega$  signature resistor while also saving board space and cost. In addition, the inrush current limit requirement of the IEEE 802.3af standard can cause large transient power dissipation in the PD. The LTC4267 is designed to allow multiple turn-on sequences without overheating the miniature 16-lead package. In the event of excessive power cycling, the LTC4267 provides thermal overload protection to keep the onboard power MOSFET within its safe operating area.

#### **OPERATION**

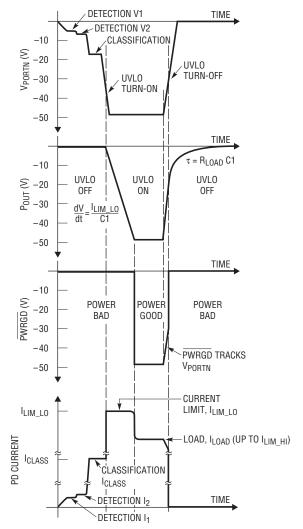

The LTC4267 PD interface has several modes of operation depending on the applied input voltage as shown in Figure 1 and summarized in Table 1. These modes satisfy the requirements defined in the IEEE 802.3af specification. The input voltage is applied to the  $V_{PORTN}$  pin and must be negative relative to the  $V_{PORTP}$  pin. Voltages in the data sheet for the PD interface portion of the LTC4267 are with respect to  $V_{PORTP}$  while the voltages for the switching regulator are referenced to PGND. It is assumed that PGND is tied to  $P_{OUT}$ . Note the use of different ground symbols throughout the data sheet.

Table 1. LTC4267 Operational Mode as a Function of Input Voltage

| INPUT VOLTAGE (VPORTN with RESPECT to VPORTP) | LTC4267 MODE OF OPERATION                            |

|-----------------------------------------------|------------------------------------------------------|

| 0V to -1.4V                                   | Inactive                                             |

| -1.5V to -9.5V**                              | $25k\Omega$ Signature Resistor Detection             |

| -9.8V to -12.4V                               | Classification Load Current Ramps up from 0% to 100% |

| -12.5V to UVLO*                               | Classification Load Current Active                   |

| UVLO* to -57V                                 | Power Applied to Switching Regulator                 |

<sup>\*</sup> $V_{PORTN}$  UVLO includes hysteresis. Rising input threshold  $\approx -36.0V$ Falling input threshold  $\approx -30.5V$

VOLTAGES WITH RESPECT TO VPORTP

$I_1 = \frac{V1 - 2 \text{ DIODE DROPS}}{25k\Omega}$

$2 = \frac{V2 - 2 \text{ DIODE DROPS}}{25k\Omega}$

I<sub>CLASS</sub> DEPENDENT ON R<sub>CLASS</sub> SELECTION

I<sub>LIM</sub> <sub>LO</sub> = 140mA (NOMINAL), I<sub>LIM</sub> <sub>HI</sub> = 375mA (NOMINAL)

$I_{LOAD} = \frac{V_{OUT}}{R_{LOAD}} \text{ (UP TO } I_{LIM\_HI}\text{)}$

Figure 1. Output Voltage, PWRGD and PD Current as a Function of Input Voltage

<sup>\*\*</sup>Measured at LTC4267 pin. The LTC4267 meets the IEEE 802.3af 10V minimum when operating with the required diode bridges.

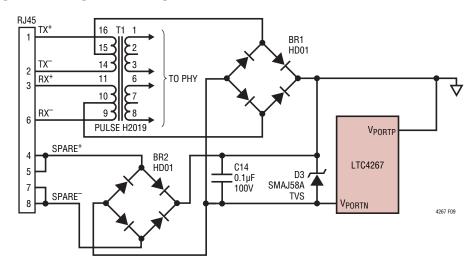

#### Series Diodes

The IEEE 802.3af-defined operating modes for a PD reference the input voltage at the RJ45 connector on the PD. The PD must be able to accept power of either polarity at each of its inputs, so it is common to install diode bridges (Figure 2). The LTC4267 takes this into account by compensating for these diode drops in the threshold points for each range of operation. A similar adjustment is made for the UVLO voltages.

#### Detection

During detection, the PSE will apply a voltage in the range of -2.8 V to -10 V on the cable and look for a  $25 k\Omega$  signature resistor. This identifies the device at the end of the cable as a PD. With the terminal voltage in this range, the LTC4267 connects an internal  $25 k\Omega$  resistor between the  $V_{PORTP}$  and  $V_{PORTN}$  pins. This precision, temperature compensated resistor presents the proper signature to alert the PSE that a PD is present and desires power to be applied. The internal low-leakage UVLO switch prevents the switching regulator circuitry from affecting the detection signature.

The LTC4267 is designed to compensate for the voltage and resistance effects of the IEEE required diode bridge.

The signature range extends below the IEEE range to accommodate the voltage drop of the two diodes. The IEEE specification requires the PSE to use a  $\Delta V/\Delta I$  measurement technique to keep the DC offset of these diodes from affecting the signature resistance measurement. However, the diode resistance appears in series with the signature resistor and must be included in the overall signature resistance of the PD. The LTC4267 compensates for the two series diodes in the signature path by offsetting the resistance so that a PD built using the LTC4267 will meet the IEEE specification.

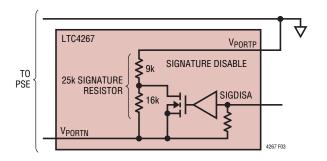

In some applications it is necessary to control whether or not the PD is detected. In this case, the  $25 k\Omega$  signature resistor can be enabled and disabled with the use of the SIGDISA pin (Figure 3). Disabling the signature via the SIGDISA pin will change the signature resistor to  $9 k\Omega$  (typical) which is an invalid signature per the IEEE 802.3af specification. This invalid signature is present for PD input voltages from -2.8 V to -10 V. If the input rises above -10 V, the signature resistor reverts to  $25 k\Omega$  to minimize power dissipation in the LTC4267. To disable the signature, tie SIGDISA to  $V_{PORTP}$ . Alternately, the SIGDISA pin can be driven high with respect to  $V_{PORTN}$ . When SIGDISA is high, all functions of the PD interface are disabled.

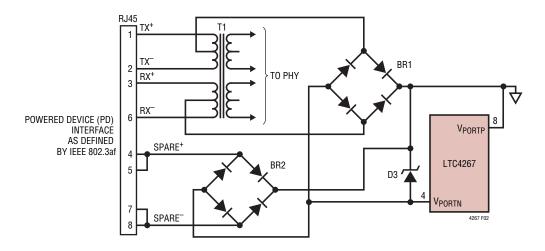

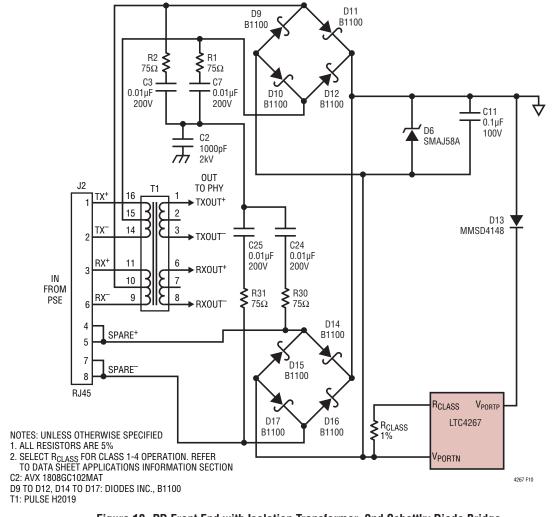

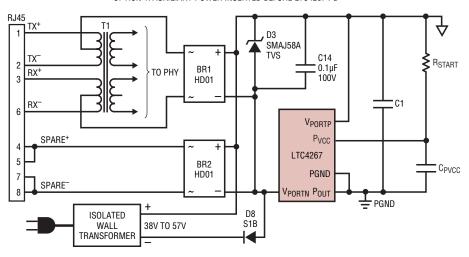

Figure 2. LTC4267 PD Front End Using Diode Bridges on Main and Spare Inputs

Figure 3. 25k Signature Resistor with Disable

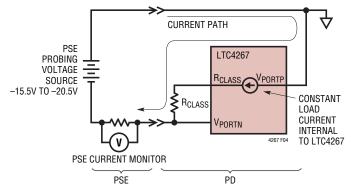

#### Classification

Once the PSE has detected a PD, the PSE may optionally classify the PD. Classification provides a method for more efficient allocation of power by allowing the PSE to identify lower power PDs and allocate less power for these devices. The IEEE 802.3af specification defines five classes (Table 2) with varying power levels. The designer selects the appropriate classification based on the power consumption of the PD. For each class, there is an associated load current that the PD asserts onto the line during classification probing. The PSE measures the PD load current to determine the proper classification and PD power requirements.

During classification (Figure 4), the PSE presents a fixed voltage between -15.5 V and -20.5 V to the PD. With the input voltage in this range, the LTC4267 asserts a load current from the  $V_{PORTP}$  pin through the  $R_{CLASS}$  resistor. The magnitude of the load current is set by the  $R_{CLASS}$  resistor. The resistor values associated with each class are shown in Table 2. Note that the switching regulator will not interfere with the classification measurement since the LTC4267 has not passed power to the regulator.

Table 2. Summary of IEEE 802.3af Power Classifications and LTC4267 R<sub>CLASS</sub> Resistor Selection

| Class | Usage    | Maximum<br>Power Levels<br>at Input of PD<br>(W) | Nominal<br>Classification<br>Load Current<br>(mA) | LTC4267 $R_{CLASS}$ Resistor $(\Omega, 1\%)$ |

|-------|----------|--------------------------------------------------|---------------------------------------------------|----------------------------------------------|

| 0     | Default  | 0.44 to 12.95                                    | <5                                                | Open                                         |

| 1     | Optional | 0.44 to 3.84                                     | 10.5                                              | 124                                          |

| 2     | Optional | 3.84 to 6.49                                     | 18.5                                              | 68.1                                         |

| 3     | Optional | 6.49 to 12.95                                    | 28                                                | 45.3                                         |

| 4     | Reserved | Reserved*                                        | 40                                                | 30.9                                         |

<sup>\*</sup>Class 4 is currently reserved and should not be used.

Figure 4. IEEE 802.3af Classification Probing

The IEEE 802.3af specification limits the classification time to 75ms because a significant amount of power is dissipated in the PD. The LTC4267 is designed to handle the power dissipation for this time period. If the PSE probing exceeds 75ms, the LTC4267 may overheat. In this situation, the thermal protection circuit will engage and disable the classification current source in order to protect the part. The LTC4267 stays in classification mode until the input voltage rises above the UVLO turn-on voltage.

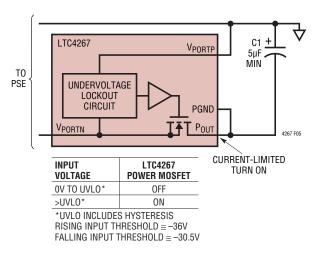

#### **V<sub>PORTN</sub>** Undervoltage Lockout

The IEEE specification dictates a maximum turn-on voltage of 42V and a minimum turn-off voltage of 30V for the PD. In addition, the PD must maintain large on-off hysteresis to prevent resistive losses in the wiring between the PSE and the PD from causing start-up oscillation. The LTC4267 incorporates an undervoltage lockout (UVLO) circuit that monitors the line voltage at V<sub>PORTN</sub> to determine when to apply power to the integrated switching regulator (Figure 5). Before the power is applied to the switching regulator, the P<sub>OUT</sub> pin is high impedance and sitting at the ground potential since there is no charge on capacitor C1. When the input voltage rises above the UVLO turn-on threshold, the LTC4267 removes the detection and classification loads and turns on the internal power MOSFET. C1 charges up under the LTC4267 current limit control and the Pout pin transitions from OV to VPORTN. This sequence is shown in Figure 1. The LTC4267 includes a hysteretic UVLO circuit on V<sub>PORTN</sub> that keeps power applied to the load until the input voltage falls below the UVLO turn-off threshold. Once the input voltage drops below –30V, the internal power MOSFET is turned off and

LINEAD

the classification current is reenabled. C1 will discharge through the PD circuitry and the  $P_{OUT}$  pin will go to a high impedance state.

Figure 5. LTC4267 V<sub>PORTN</sub> Undervoltage Lockout

#### **Input Current Limit**

IEEE 802.3af specifies a maximum inrush current and also specifies a minimum load capacitor between the  $V_{PORTP}$  and  $P_{OUT}$  pins. To control turn-on surge current in the system, the LTC4267 integrates a dual level current limit circuit with an onboard power MOSFET and sense resistor to provide a complete inrush control circuit without additional external components. At turn-on, the LTC4267 will limit the input current to the low level, allowing the load capacitor to ramp up to the line voltage in a controlled manner.

The LTC4267 has been specifically designed to interface with legacy PSEs which do not meet the inrush current requirement of the IEEE 802.3af specification. At turn-on the LTC4267 current limit is set to the lower level. After C1 is charged up and the P<sub>OUT</sub> – V<sub>PORTN</sub> voltage difference is below the power good threshold, the LTC4267 switches to the high level current limit. The dual level current limit allows legacy PSEs with limited current sourcing capability to power up the PD while also allowing the PD to draw full power from an IEEE 802.3af PSE. The dual level current limit also allows use of arbitrarily large load capacitors. The IEEE 802.3af specification mandates that at turn-on the PD not exceed the inrush current limit for more than 50ms. The LTC4267 is not restricted to the 50ms time

limit because the load capacitor is charged with a current below the IEEE inrush current limit specification.

As the LTC4267 switches from the low to high level current limit, the current will increase momentarily. This current spike is a result of the LTC4267 charging the last 1.5V at the high level current limit. When charging a  $10\mu F$  capacitor, the current spike is typically  $100\mu s$  wide and 125% of the nominal low level current limit.

The LTC4267 stays in the high level current limit mode until the input voltage drops below the UVLO turn-off threshold. This dual level current limit provides the system designer with the flexibility to design PDs which are compatible with legacy PSEs while also being able to take advantage of the higher power allocation available in an IEEE 802.3af system.

During the current limited turn on, a large amount of power is dissipated in the power MOSFET. The LTC4267 PD interface is designed to accept this thermal load and is thermally protected to avoid damage to the onboard power MOSFET. Note that in order to adhere to the IEEE 802.3af standard, it is necessary for the PD designer to ensure the PD steady state power consumption falls within the limits shown in Table 2. In addition, the steady state current must be less than I<sub>LIM</sub> HI.

#### **Power Good**

The LTC4267 PD Interface includes a power good circuit (Figure 6) that is used to indicate that load capacitor C1 is fully charged and that the switching regulator can start operation. The power good circuit monitors the voltage across the internal UVLO power MOSFET and PWRGD is asserted when the voltage falls below 1.5V. The power good circuit includes hysteresis to allow the LTC4267 to operate near the current limit point without inadvertently disabling PWRGD. The MOSFET voltage must increase to 3V before PWRGD is disabled.

If a sudden increase in voltage appears on the input line, this voltage step will be transferred through capacitor C1 and appear across the power MOSFET. The response of the LTC4267 will depend on the magnitude of the voltage step, the rise time of the step, the value of capacitor C1 and the switching regulator load. For fast rising inputs,

Figure 6. LTC4267 Power Good

the LTC4267 will attempt to quickly charge capacitor C1 using an internal secondary current limit circuit. In this scenario, the PSE current limit should provide the overall limit for the circuit. For slower rising inputs, the 375mA current limit in the LTC4267 will set the charge rate of the capacitor C1. In either case, the PWRGD signal may go inactive briefly while the capacitor is charged up to the new line voltage. In the design of a PD, it is necessary to determine if a step in the input voltage will cause the PWRGD signal to go inactive and how to respond to this event. In some designs, it may be desirable to filter the PWRGD signal so that intermittent power bad conditions are ignored. Figure 7 demonstrates a method to insert a lowpass filter on the power good interface.

For PD designs that use a large load capacitor and also consume a lot of power, it is important to delay activation of the switching regulator with the PWRGD signal. If the regulator is not disabled during the current-limited turn-on sequence, the PD circuitry will rob current intended for charging up the load capacitor and create a slow rising input, possibly causing the LTC4267 to go into thermal shutdown.

The  $\overline{PWRGD}$  pin connects to an internal open drain, 100V transistor capable of sinking 1mA. Low impedance to  $V_{PORTN}$  indicates power is good.  $\overline{PWRGD}$  is high impedance during signature and classification probing and in the event of a thermal overload. During turn-off,  $\overline{PWRGD}$  is deactivated when the input voltage drops below 30V. In addition,  $\overline{PWRGD}$  may go active briefly at turn-on for fast rising input waveforms.  $\overline{PWRGD}$  is referenced to the  $V_{PORTN}$  pin and when active, will be near the  $V_{PORTN}$  potential. Connect the  $\overline{PWRGD}$  pin to the switching regulator circuitry as shown in Figure 7.

Figure 7. Power Good Interface Examples

#### **PD Interface Thermal Protection**

The LTC4267 PD Interface includes thermal overload protection in order to provide full device functionality in a miniature package while maintaining safe operating temperatures. Several factors create the possibility of significant power dissipation within the LTC4267. At turn-on, before the load capacitor has charged up, the instantaneous power dissipated by the LTC4267 can be as much as 10W. As the load capacitor charges up, the power dissipation in the LTC4267 will decrease until it reaches a steady-state value dependent on the DC load current. The size of the load capacitor determines how fast the power dissipation in the LTC4267 will subside. At room temperature, the LTC4267 can typically handle load capacitors as large as 800µF without going into thermal shutdown. With large load capacitors, the LTC4267 die temperature will increase by as much as 50°C during a single turn-on sequence. If for some reason power were removed from the part and then quickly reapplied so that the LTC4267 had to charge up the load capacitor again, the temperature rise would be excessive if safety precautions were not implemented.

The LTC4267 PD interface protects itself from thermal damage by monitoring the die temperature. If the die

temperature exceeds the overtemperature trip point, the current is reduced to zero and very little power is dissipated in the part until it cools below the overtemperature set point. Once the LTC4267 has charged up the load capacitor and the PD is powered and running, there will be minor residual heating due to the DC load current of the PD flowing through the internal MOSFET. The DHC package offers superior thermal performance by including an exposed pad that is soldered to an electrically isolated heat sink on the printed circuit board.

During classification, excessive heating of the LTC4267 can occur if the PSE violates the 75ms probing time limit. To protect the LTC4267, thermal overload circuitry will disable classification current if the die temperature exceeds the overtemperature trip point. When the die cools down below the trip point, classification current is reenabled.

The PD is designed to operate at a high ambient temperature and with the maximum allowable supply (57V). However, there is a limit to the size of the load capacitor that can be charged up before the LTC4267 reaches the overtemperature trip point. Hitting the overtemperature trip point intermittently does not harm the LTC4267, but it will delay the completion of capacitor charging. Capacitors up to 200µF can be charged without a problem over the full operating temperature range.

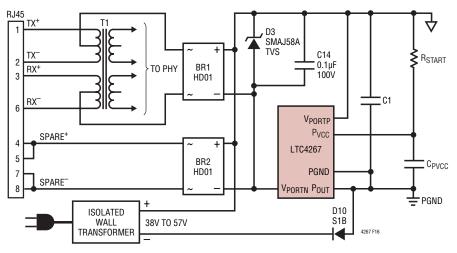

## **Switching Regulator Main Control Loop**

Due to space limitations, the basics of current mode DC/DC conversion will not be discussed here. The reader is referred to the detail treatment in Application Note 19 or in texts such as Abraham Pressman's *Switching Power Supply Design*.

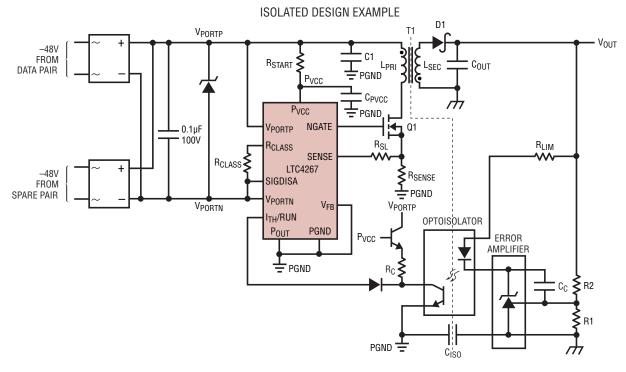

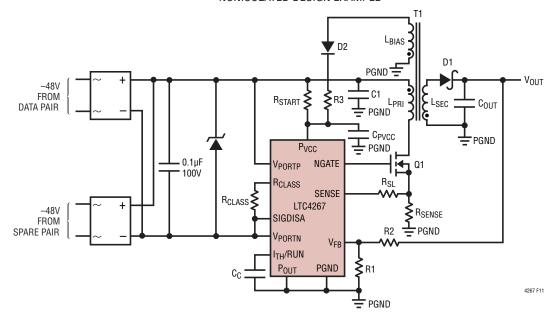

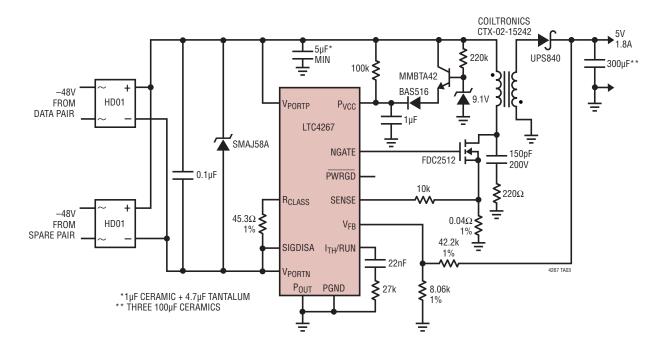

In a Power over Ethernet System, the majority of applications involve an isolated power supply design. This means that the output power supply does not have any DC electrical path to the PD interface or the switching regulator primary. The DC isolation is achieved typically through a transformer in the forward path and an optoisolator in the feedback path or a third winding in the transformer. The typical application circuit shown on the front page of the datasheet represents an isolated design using an optoisolator. In applications where a nonisolated topology is desired, the LTC4267 features a feedback port

and an internal error amplifier that can be enabled for this specific application.

In the typical application circuit (Figure 11), the isolated topology employs an external resistive voltage divider to present a fraction of the output voltage to an external error amplifier. The error amplifier responds by pulling an analog current through the input LED on an optoisolator. The collector of the optoisolator output presents a corresponding current into the  $I_{TH}/RUN$  pin via a series diode. This method generates a feedback voltage on the  $I_{TH}/RUN$  pin while maintaining isolation.

The voltage on the  $I_{TH}/RUN$  pin controls the pulse-width modulator formed by the oscillator, current comparator, and RS latch. Specifically, the voltage at the  $I_{TH}/RUN$  pin sets the current comparator's trip threshold. The current comparator monitors the voltage across a sense resistor in series with the source terminal of the external N-Channel MOSFET. The LTC4267 turns on the external power MOSFET when the internal free-running 200kHz oscillator sets the RS latch. It turns off the MOSFET when the current comparator resets the latch or when 80% duty cycle is reached, whichever happens first. In this way, the peak current levels through the flyback transformer's primary and secondary are controlled by the  $I_{TH}/RUN$  voltage.

In applications where a nonisolated topology is desirable (Figure 11), an external resistive voltage divider can present a fraction of the output voltage directly to the  $V_{FB}$  pin of the LTC4267. The divider must be designed so when the output is at its desired voltage, the  $V_{FB}$  pin voltage will equal the 800mV onboard internal reference. The internal error amplifier responds by driving the  $I_{TH}/RUN$  pin. The LTC4267 switching regulator performs in a similar manner as described previously.

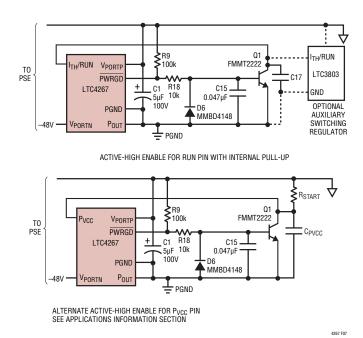

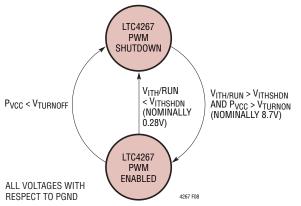

#### Regulator Start-Up/Shutdown

The LTC4267 switching regulator has two shutdown mechanisms to enable and disable operation: an undervoltage lockout on the  $P_{VCC}$  supply pin and a forced shutdown whenever external circuitry drives the  $I_{TH}/RUN$  pin low. The LTC4267 switcher transitions into and out of shutdown according to the state diagram (Figure 8). It is important not to confuse the undervoltage lockout of the PD interface at  $V_{PORTN}$  with that of the switching regulator at  $P_{VCC}$ . They are independent functions.

The undervoltage lockout mechanism on  $P_{VCC}$  prevents the LTC4267 switching regulator from trying to drive the external N-Channel MOSFET with insufficient gate-to-

Figure 8. LTC4267 Switching Regulator Start-Up/Shutdown State Diagram

source voltage. The voltage at the  $P_{VCC}$  pin must exceed  $V_{TURNON}$  (nominally 8.7V with respect to PGND) at least momentarily to enable operation. The  $P_{VCC}$  voltage must fall to  $V_{TURNOFF}$  (nominally 5.7V with respect to PGND) before the undervoltage lockout disables the switching regulator. This wide UVLO hysteresis range supports applications where a bias winding on the flyback transformer is used to increase the efficiency of the LTC4267 switching regulator.

The  $I_{TH}/RUN$  can be driven below  $V_{ITHSHDN}$  (nominally 0.28V with respect to PGND) to force the LTC4267 switching regulator into shutdown. An internal 0.3µA current source always tries to pull the  $I_{TH}/RUN$  pin towards  $P_{VCC}$ . When the  $I_{TH}/RUN$  pin voltage is allowed to exceed  $V_{ITHSHDN}$  and  $P_{VCC}$  exceeds  $V_{TURNON}$ , the LTC4267 switching regulator begins to operate and an internal clamp immediately pulls the  $I_{TH}/RUN$  pin to about 0.7V. In operation, the  $I_{TH}/RUN$  pin voltage will vary from roughly 0.7V to 1.9V to represent current comparator thresholds from zero to maximum.

#### Internal Soft-Start

An internal soft-start feature is enabled whenever the LTC4267 switching regulator comes out of shutdown. Specifically, the  $I_{TH}/RUN$  voltage is clamped and is prevented from reaching maximum until 1.4ms have passed. This allows the input current of the PD to rise in a smooth and controlled manner on start-up and stay within the current limit requirement of the LTC4267 interface.

#### **Adjustable Slope Compensation**

The LTC4267 switching regulator injects a  $5\mu A$  peak current ramp out through its SENSE pin which can be used for slope compensation in designs that require it. This current ramp is approximately linear and begins at zero current at 6% duty cycle, reaching peak current at 80% duty cycle. Programming the slope compensation via a series resistor is discussed in the External Interface and Component Selection section.

#### EXTERNAL INTERFACE AND COMPONENT SELECTION

#### **Input Interface Transformer**

Nodes on an Ethernet network commonly interface to the outside world via an isolation transformer (Figure 9). For PoE devices, the isolation transformer must include a center tap on the media (cable) side. Proper termination is required around the transformer to provide correct impedance matching and to avoid radiated and conducted emissions. Transformer vendors such as Bel Fuse, Coilcraft, Pulse and Tyco (Table 3) can provide assistance with selection of an appropriate isolation transformer and proper termination methods. These vendors have transformers specifically designed for use in PD applications.

**Table 3. Power over Ethernet Transformer Vendors**

| VENDOR            | CONTACT INFORMATION                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| Bel Fuse Inc.     | 206 Van Vorst Street<br>Jersey City, NJ 07302<br>Tel: 201-432-0463<br>FAX: 201-432-9542<br>http://www.belfuse.com     |

| Coilcraft, Inc.   | 1102 Silver Lake Road<br>Cary, IL 60013<br>Tel: 847-639-6400<br>FAX: 847-639-1469<br>http://www.coilcraft.com         |

| Pulse Engineering | 12220 World Trade Drive<br>San Diego, CA 92128<br>Tel: 858-674-8100<br>FAX: 858-674-8262<br>http://www.pulseeng.com   |

| Tyco Electronics  | 308 Constitution Drive Menlo Park, CA 94025-1164 Tel: 800-227-7040 FAX: 650-361-2508 http://www.circuitprotection.com |

#### **Diode Bridge**

IEEE 802.3af allows power wiring in either of two configurations: on the TX/RX wires or via the spare wire pairs in the RJ45 connector. The PD is required to accept power in either polarity on either the main or spare inputs; therefore it is common to install diode bridges on both inputs in order to accommodate the different wiring configurations. Figure 9 demonstrates an implementation of these diode bridges. The IEEE 802.3af specification also mandates that the leakage back through the unused bridge be less than 28μA when the PD is powered with 57V.

The IEEE standard includes an AC impedance requirement in order to implement the AC disconnect function. Capacitor C14 in Figure 9 is used to meet this AC impedance requirement. A  $0.1\mu F$  capacitor is recommended for this application.

The LTC4267 has several different modes of operation based on the voltage present between  $V_{PORTN}$  and  $V_{PORTP}$  pins. The forward voltage drop of the input diodes in a PD design subtracts from the input voltage and will affect the transition point between modes. When using the LTC4267, it is necessary to pay close attention to this forward voltage drop. Selection of oversized diodes will help keep the PD thresholds from exceeding IEEE specifications.

The input diode bridge of a PD can consume over 4% of the available power in some applications. It may be desirable to use Schottky diodes in order to reduce power loss. However, if the standard diode bridge is replaced with a Schottky bridge, the transition points between the modes will be affected. Figure 10 shows a technique for using Schottky diodes while maintaining proper threshold points to meet IEEE 802.3af compliance. D13 is added to compensate for the change in UVLO turn-on voltage caused by the Schottky diodes and consumes little power.

# Classification Resistor Selection (R<sub>CLASS</sub>)

The IEEE specification allows classifying PDs into four distinct classes with class 4 being reserved for future use (Table 2). An external resistor connected from  $R_{CLASS}$  to  $V_{PORTN}$  (Figure 4) sets the value of the load current. The designer should determine which power category the PD

falls into and then select the appropriate value of  $R_{CLASS}$  from Table 2. If a unique load current is required, the value of  $R_{CLASS}$  can be calculated as:

$R_{CLASS} = 1.237V/(I_{DESIRED} - I_{IN\_CLASS})$

where  $I_{IN\_CLASS}$  is the LTC4267 IC supply current during classification and is given in the electrical specifications. The  $R_{CLASS}$  resistor must be 1% or better to avoid degrading the overall accuracy of the classification circuit. Resistor power dissipation will be 50mW maximum and is transient so heating is typically not a concern. In order to maintain loop stability, the layout should minimize capacitance at the  $R_{CLASS}$  node. The classification circuit can be disabled by floating the  $R_{CLASS}$  pin. The  $R_{CLASS}$  pin should not be shorted to  $V_{PORTN}$  as this would force the LTC4267 classification circuit to attempt to source very large currents and quickly go into thermal shutdown.

#### **Power Good Interface**

The  $\overline{PWRGD}$  signal is controlled by a high voltage, opendrain transistor. The designer has the option of using this signal to enable the onboard switching regulator through the  $I_{TH}/RUN$  or the  $P_{VCC}$  pins. Examples of active-high interface circuits for controlling the switching regulator are shown in Figure 7.

In some applications, it is desirable to ignore intermittent power bad conditions. This can be accomplished by including capacitor C15 in Figure 7 to form a lowpass filter. With the components shown, power bad conditions less than about 200 $\mu$ s will be ignored. Conversely, in other applications it may be desirable to delay assertion of  $\overline{PWRGD}$  to the switching regulator using  $C_{PVCC}$  or C17 as shown in Figure 7.

It is recommended that the designer use the power good signal to enable the switching regulator. Using PWRGD ensures the capacitor C1 has reached within 1.5V of the final value and is ready to accept a load. The LTC4267 is designed with wide power good hysteresis to handle sudden fluctuations in the load voltage and current without prematurely shutting off the switching regulator. Please refer to the Power-Up Sequencing of the Application Information section.

Figure 9. PD Front End with Isolation Transformer, Diode Bridges and Capacitor

Figure 10. PD Front End with Isolation Transformer, 2nd Schottky Diode Bridge

LINEAR TECHNOLOGY

#### Signature Disable Interface

To disable the  $25k\Omega$  signature resistor, connect SIGDISA pin to the  $V_{PORTP}$  pin. Alternately, SIGDISA pin can be driven high with respect to  $V_{PORTN}$ . An example of a signature disable interface is shown in Figure 16, option 2. Note that the SIGDISA input resistance is relatively large and the threshold voltage is fairly low. Because of high voltages present on the printed circuit board, leakage currents from the  $V_{PORTP}$  pin could inadvertently pull SIGDISA high. To ensure trouble-free operation, use high voltage layout techniques in the vicinity of SIGDISA. If unused, connect SIGDISA to  $V_{PORTN}$ .

#### **Load Capacitor**

The IEEE 802.3af specification requires that the PD maintain a minimum load capacitance of  $5\mu F$  (provided by C1 in Figure 11). It is permissible to have a much larger load capacitor and the LTC4267 can charge very large load capacitors before thermal issues become a problem. The load capacitor must be large enough to provide sufficient energy for proper operation of the switching regulator. However, the capacitor must not be too large or the PD design may violate IEEE 802.3af requirements.

If the load capacitor is too large, there can be a problem with inadvertent power shutdown by the PSE. Consider the following scenario. If the PSE is running at -57V (maximum allowed) and the PD has detected and powered up, the load capacitor will be charged to nearly -57V. If for some reason the PSE voltage is suddenly reduced to -44V (minimum allowed), the input bridge will reverse bias and the PD power will be supplied by the load capacitor. Depending on the size of the load capacitor and the DC load of the PD, the PD will not draw any power for a period of time. If this period of time exceeds the IEEE 802.3af 300ms disconnect delay, the PSE will remove power from the PD. For this reason, it is necessary to ensure that inadvertent shutdown cannot occur.

Very small output capacitors (≤10µF) will charge very quickly in current limit. The rapidly changing voltage at the output may reduce the current limit temporarily, causing the capacitor to charge at a somewhat reduced rate. Conversely, charging a very large capacitor may cause the current limit to increase slightly. In either case, once the

output voltage reaches its final value, the input current limit will be restored to its nominal value.

The load capacitor can store significant energy when fully charged. The design of a PD must ensure that this energy is not inadvertently dissipated in the LTC4267. The polarity-protection diode(s) prevent an accidental short on the cable from causing damage. However, if the  $V_{PORTN}$  pin is shorted to  $V_{PORTP}$  inside the PD while the capacitor is charged, current will flow through the parasitic body diode of the internal MOSFET and may cause permanent damage to the LTC4267.

#### **Maintain Power Signature**

In an IEEE 802.3af system, the PSE uses the maintain power signature (MPS) to determine if a PD continues to require power. The MPS requires the PD to periodically draw at least 10mA and also have an AC impedance less than  $26.25k\Omega$  in parallel with  $0.05\mu F$ . If either the DC current is less than 10mA or the AC impedance is above  $26.25k\Omega$ , the PSE may disconnect power. The DC current must be less than 5mA and the AC impedance must be above  $2M\Omega$  to guarantee power will be removed.

# **Selecting Feedback Resistor Values**

The regulated output voltage of the switching regulator is determined by the resistor divider across  $V_{OUT}$  (R1 and R2 in Figure 11) and the error amplifier reference voltage  $V_{REF}$ . The ratio of R2 to R1 needed to produce the desired voltage can be calculated as:

$$R2 = R1 \bullet (V_{OUT} - V_{REF})/V_{REF}$$

In an isolated power supply application,  $V_{REF}$  is determined by the designer's choice of an external error amplifier. Commercially available error amplifiers or programmable shunt regulators may include an internal reference of 1.25V or 2.5V. Since the LTC4267 internal reference and error amplifier are not used in an isolated design, tie the  $V_{FB}$  pin to PGND.

In a nonisolated power supply application, the LTC4267 onboard internal reference and error amplifier can be used. The resistor divider output can be tied directly to the  $V_{FB}$  pin. The internal reference of the LTC4267 is 0.8V nominal.

Choose resistance values for R1 and R2 to be as large as possible to minimize any efficiency loss due to the static current drawn from  $V_{OUT}$ , but just small enough so that when  $V_{OUT}$  is in regulation, the error caused by the nonzero input current from the output of the resistor divider to the error amplifier pin is less than 1%.

## **Error Amplifier and Optoisolator Considerations**

In an isolated topology, the selection of the external error amplifier depends on the output voltage of the switching regulator. Typical error amplifiers include a voltage reference of either 1.25V or 2.5V. The output of the amplifier and the amplifier upper supply rail are often tied together internally. The supply rail is usually specified with a wide upper voltage range, but it is not allowed to fall below the reference voltage. This can be a problem in an isolated switcher design if the amplifier supply voltage is not properly managed. When the switcher load current decreases and the output voltage rises, the error amplifier responds by pulling more current through the LED. The LED voltage can be as large as 1.5V, and along with R<sub>I IM</sub>, reduces the supply voltage to the error amplifier. If the error amp does not have enough headroom, the voltage drop across the LED and R<sub>I IM</sub> may shut the amplifier off momentarily, causing a lock-up condition in the main loop. The switcher will undershoot and not recover until the error amplifier releases its sink current. Care must be taken to select the reference voltage and  $R_{LIM}$  value so that the error amplifier always has enough headroom. An alternate solution that avoids these problems is to utilize the LT1431 or LT4430 where the output of the error amplifier and amplifier supply rail are brought out to separate pins.

The PD designer must also select an optoisolator such that its bandwidth is sufficiently wider than the bandwidth of the main control loop. If this step is overlooked, the main control loop may be difficult to stabilize. The output collector resistor of the optoisolator can be selected for an increase in bandwidth at the cost of a reduction in gain of this stage.

# **Output Transformer Design Considerations**

Since the external feedback resistor divider sets the output voltage, the PD designer has relative freedom in

selecting the transformer turns ratio. The PD designer can use simple ratios of small integers (i.e. 1:1, 2:1, 3:2) which yields more freedom in setting the total turns and mutual inductance and may allow the use of an off the shelf transformer.

Transformer leakage inductance on either the primary or secondary causes a voltage spike to occur after the output switch (Q1 in Figure 11) turns off. The input supply voltage plus the secondary-to-primary referred voltage of the flyback pulse (including leakage spike) must not exceed the allowed external MOSFET breakdown rating. This spike is increasingly prominent at higher load currents, where more stored energy must be dissipated. In some cases, a "snubber" circuit will be required to avoid overvoltage breakdown at the MOSFET's drain node. Application Note 19 is a good reference for snubber design.

#### **Current Sense Resistor Consideration**

The external current sense resistor (R<sub>SENSE</sub> in Figure 11) allows the designer to optimize the current limit behavior for a particular application. As the current sense resistor is varied from several ohms down to tens of milliohms, peak swing current goes from a fraction of an ampere to several amperes. Care must be taken to ensure proper circuit operation, especially for small current sense resistor values.

Choose R<sub>SENSE</sub> such that the switching current exercises the entire range of the I<sub>TH</sub>/RUN voltage. The nominal voltage range is 0.7V to 1.9V and R<sub>SENSF</sub> can be determined by experiment. The main loop can be temporarily stabilized by connecting a large capacitor on the power supply. Apply the maximum load current allowable at the power supply output based on the class of the PD. Choose R<sub>SENSE</sub> such that I<sub>TH</sub>/RUN approaches 1.9V. Finally, exercise the output load current over the entire operating range and ensure that I<sub>TH</sub>/RUN voltage remains within the 0.7V to 1.9V range. Layout is critical around the R<sub>SENSE</sub> resistor. For example, a  $0.020\Omega$  sense resistor, with one milliohm  $(0.001\Omega)$  of parasitic resistance will cause a 5% reduction in peak switch current. The resistance of printed circuit copper traces cannot necessarily be ignored and good layout techniques are mandatory.

LINEAR TECHNOLOGY

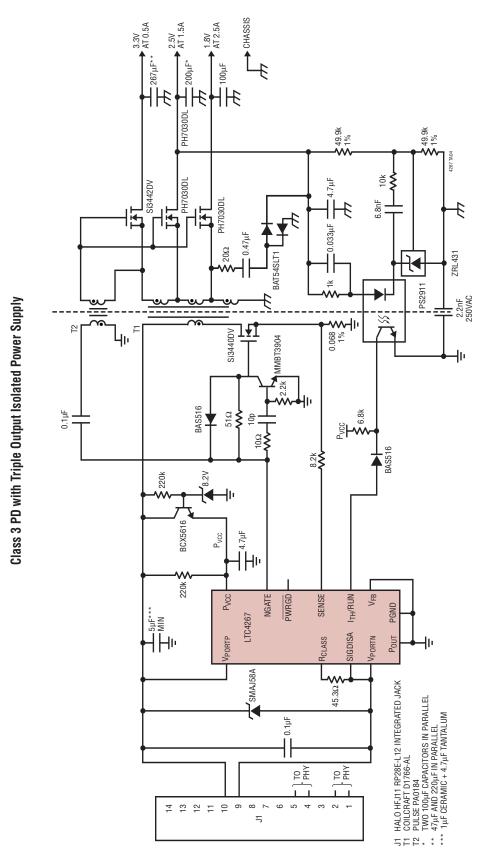

#### NONISOLATED DESIGN EXAMPLE

Figure 11. Typical LTC4267 Application Circuits

#### **Programmable Slope Compensation**

The LTC4267 switching regulator injects a ramping current through its SENSE pin into an external slope compensation resistor (R<sub>SI</sub> in Figure 11). This current ramp starts at zero after the NGATE pin has been high for the LTC4267's minimum duty cycle of 6%. The current rises linearly towards a peak of 5µA at the maximum duty cycle of 80%, shutting off once the NGATE pin goes low. A series resistor (R<sub>SI</sub>) connecting the SENSE pin to the current sense resistor (R<sub>SENSE</sub>) develops a ramping voltage drop. From the perspective of the LTC4267 SENSE pin, this ramping voltage adds to the voltage across the sense resistor, effectively reducing the current comparator threshold in proportion to duty cycle. This stabilizes the control loop against subharmonic oscillation. The amount of reduction in the current comparator threshold ( $\Delta V_{SENSE}$ ) can be calculated using the following equation:

$\Delta V_{SFNSF} = 5\mu A \cdot R_{SI} \cdot [(Duty Cycle - 6\%)/74\%]$

Note: The LTC4267 enforces 6% < Duty Cycle < 80%.

Designs not needing slope compensation may replace  $R_{SL}$  with a short-circuit.

# **Applications Employing a Third Transformer Winding**

A standard operating topology may employ a third winding on the transformer's primary side that provides power to the LTC4267 switching regulator via its  $P_{VCC}$  pin (Figure 11). However, this arrangement is not inherently self-starting. Start-up is usually implemented by the use of an external "trickle-charge" resistor ( $R_{START}$ ) in conjunction with the internal wide hysteresis undervoltage lockout circuit that monitors the  $P_{VCC}$  pin voltage.

$R_{START}$  is connected to  $V_{PORTP}$  and supplies a current, typically 100µA, to charge  $C_{PVCC}$ . After some time, the voltage on  $C_{PVCC}$  reaches the  $P_{VCC}$  turn-on threshold. The LTC4267 switching regulator then turns on abruptly and draws its normal supply current. The NGATE pin begins switching and the external MOSFET (Q1) begins to deliver power. The voltage on  $C_{PVCC}$  begins to decline as the switching regulator draws its normal supply current, which exceeds the delivery from  $R_{START}$ . After some time, typically tens of milliseconds, the output voltage approaches the desired value. By this time, the third transformer winding

is providing virtually all the supply current required by the LTC4267 switching regulator.

One potential design pitfall is under-sizing the value of capacitor  $C_{PVCC}$ . In this case, the normal supply current drawn through  $P_{VCC}$  will discharge  $C_{PVCC}$  rapidly before the third winding drive becomes effective. Depending on the particular situation, this may result in either several off-on cycles before proper operation is reached or permanent relaxation oscillation at the  $P_{VCC}$  node.

Resistor  $R_{START}$  should be selected to yield a worst-case minimum charging current greater that the maximum rated LTC4267 start-up current to ensure there is enough current to charge  $C_{PVCC}$  to the  $P_{VCC}$  turn-on threshold.  $R_{START}$  should also be selected large enough to yield a worst-case maximum charging current less than the minimum-rated  $P_{VCC}$  supply current, so that in operation, most of the  $P_{VCC}$  current is delivered through the third winding. This results in the highest possible efficiency.

Capacitor C<sub>PVCC</sub> should then be made large enough to avoid the relaxation oscillation behavior described previously. This is difficult to determine theoretically as it depends on the particulars of the secondary circuit and load behavior. Empirical testing is recommended.

The third transformer winding should be designed so that its output voltage, after accounting for the forward diode voltage drop, exceeds the maximum  $P_{VCC}$  turn-off threshold. Also, the third winding's nominal output voltage should be at least 0.5V below the minimum rated  $P_{VCC}$  clamp voltage to avoid running up against the LTC4267 shunt regulator, needlessly wasting power.

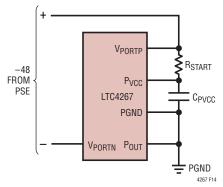

# **P<sub>VCC</sub> Shunt Regulator**

In applications including a third transformer winding, the internal  $P_{VCC}$  shunt regulator serves to protect the LTC4267 switching regulator from overvoltage transients as the third winding is powering up.

If a third transformer winding is undesirable or unavailable, the shunt regulator allows the LTC4267 switching regulator to be powered through a single dropping resistor from  $V_{PORTP}$  as shown in Figure 12. This simplicity comes at the expense of reduced efficiency due to static power dissipation in the  $R_{START}$  dropping resistor.

The shunt regulator can sink up to 5mA through the  $P_{VCC}$  pin to PGND. The values of  $R_{START}$  and  $C_{PVCC}$  must be selected for the application to withstand the worst-case load conditions and drop on  $P_{VCC}$ , ensuring that the  $P_{VCC}$  turn-off threshold is not reached.  $C_{PVCC}$  should be sized sufficiently to handle the switching current needed to drive NGATE while maintaining minimum switching voltage.

Figure 12. Powering the LTC4267 Switching Regulator via the Shunt Regulator

## **External Preregulator**

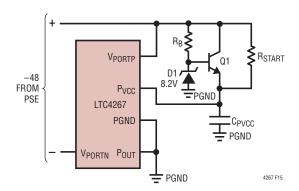

The circuit in Figure 13 shows a third way to power the LTC4267 switching regulator circuit. An external series preregulator consists of a series pass transistor Q1, zener diode D1, and a bias resistor R<sub>B</sub>. The preregulator holds P<sub>VCC</sub> at 7.6V nominal, well above the maximum rated P<sub>VCC</sub> turn-off threshold of 6.8V. Resistor R<sub>START</sub> momentarily charges the P<sub>VCC</sub> node up to the P<sub>VCC</sub> turn-on threshold, enabling the switching regulator. The voltage on C<sub>PVCC</sub> begins to decline as the switching regulator draws its normal supply current, which exceeds the delivery of R<sub>START</sub>. After some time, the output voltage approaches the desired value. By this time, the pass transistor Q1 catches the declining voltage on the P<sub>VCC</sub> pin, and provides virtually all the supply current required by the LTC4267 switching regulator. C<sub>PVCC</sub> should be sized sufficiently to handle the switching current needed to drive NGATE while maintaining minimum switching voltage.

The external preregulator has improved efficiency over the simple resistor-shunt regulator method mentioned previously.  $R_B$  can be selected so that it provides a small current necessary to maintain the zener diode voltage and the maximum possible base current Q1 will encounter. The

actual current needed to power the LTC4267 switching regulator goes through Q1 and  $P_{VCC}$  sources current on an "as-needed" basis. The static current is then limited only to the current through  $R_B$  and D1.

Figure 13. Powering the LTC4267 Switching Regulator with an External Preregulator

# **Compensating the Main Loop**

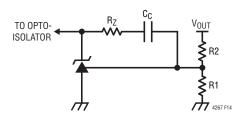

In an isolated topology, the compensation point is typically chosen by the components configured around the external error amplifier. Shown in Figure 14, a series RC network is connected from the compare voltage of the error amplifier to the error amplifier output. In PD designs where transient load response is not critical, replace  $R_Z$  with a short. The product of R2 and  $C_C$  should be sufficiently large to ensure stability. When fast settling transient response is critical, introduce a zero set by  $R_Z C_C$ . The PD designer must ensure that the faster settling response of the output voltage does not compromise loop stability.

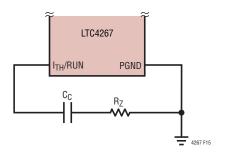

In a nonisolated design, the LTC4267 incorporates an internal error amplifier where the  $I_{TH}/RUN$  pin serves as a compensation point. In a similar manner, a series RC network can be connected from  $I_{TH}/RUN$  to PGND as shown in Figure 15.  $C_C$  and  $R_Z$  are chosen for optimum load and line transient response.

Figure 14. Main Loop Compensation for an Isolated Design

Figure 15. Main Loop Compensation for a Nonisolated Design

#### **Selecting the Switching Transistor**

With the N-channel power MOSFET driving the primary of the transformer, the inductance will cause the drain of the MOSFET to traverse twice the voltage across  $V_{PORTP}$  and PGND. The LTC4267 operates with a maximum supply of -57V; thus the MOSFET must be rated to handle 114V or more with sufficient design margin. Typical transistors have 150V ratings while some manufacturers have developed 120V rated MOSFETs specifically for Power-over-Ethernet applications.