#### Features

- Available with any-frequency output

Available CMOS, LVPECL, frequencies from 10 to 810 MHz

- 3rd generation DSPLL<sup>®</sup> with superior jitter performance: 1 ps max jitter

- Better frequency stability than SAWbased oscillators

- Internal fundamental mode crystal ensures high reliability

#### Applications

- SONET/SDH (OC-3/12/48)

- Networking

- SD/HD SDI/3G SDI video

#### Description

- Test and measurement

- Storage

FPGA/ASIC clock generation

LVDS, and CML outputs

Pb-free/RoHS-compliant

-40 to +85 °C operating

package and pinout

temperature range

Industry-standard 5 x 7 mm

3.3, 2.5, and 1.8 V supply options

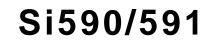

The Si590/591 XO utilizes Silicon Laboratories' advanced DSPLL<sup>®</sup> circuitry to provide a low jitter clock at high frequencies. The Si590/591 supports any frequency from 10 to 810 MHz. Unlike a traditional XO, where a unique crystal is required for each output frequency, the Si590/591 uses one fixed crystal to provide a wide range of output frequencies. This IC based approach allows the crystal resonator to provide exceptional frequency stability and reliability. In addition, DSPLL clock synthesis provides superior supply noise rejection, simplifying the task of generating low jitter clocks in noisy environments typically found in communication systems. The Si590/591 IC based XO is factory configurable for a wide variety of user specifications including frequency, supply voltage, output format, and stability. Specific configurations are factory programmed at time of shipment, thereby eliminating long lead times associated with custom oscillators.

#### Functional Block Diagram

# **1. Electrical Specifications**

#### **Table 1. Recommended Operating Conditions**

| Parameter                       | Symbol          | Test Condition  | Min                    | Тур | Max  | Units |

|---------------------------------|-----------------|-----------------|------------------------|-----|------|-------|

| Supply Voltage <sup>1</sup>     | V <sub>DD</sub> | 3.3 V option    | 2.97                   | 3.3 | 3.63 |       |

|                                 |                 | 2.5 V option    | 2.25                   | 2.5 | 2.75 | V     |

|                                 |                 | 1.8 V option    | 1.71                   | 1.8 | 1.89 |       |

| Supply Current                  | I <sub>DD</sub> | Output enabled  |                        |     |      |       |

|                                 |                 | LVPECL          |                        | 110 | 125  |       |

|                                 |                 | CML             |                        | 100 | 110  |       |

|                                 |                 | LVDS            |                        | 90  | 100  | mA    |

|                                 |                 | CMOS            | —                      | 80  | 90   |       |

|                                 |                 | Tristate mode   | —                      | 60  | 75   | -     |

| Output Enable (OE) <sup>2</sup> |                 | V <sub>IH</sub> | 0.75 x V <sub>DD</sub> | _   |      | V     |

|                                 |                 | V <sub>IL</sub> | —                      |     | 0.5  |       |

| Operating Temperature Range     | T <sub>A</sub>  |                 | -40                    |     | 85   | ٥C    |

| Notos:                          | •               |                 | •                      |     | •    | •     |

#### Notes:

1. Selectable parameter specified by part number. See Section 3. "Ordering Information" on page 7 for further details.

2. OE pin includes an internal 17 k $\Omega$  pullup resistor to V<sub>DD</sub> for output enable active high or a 17 k $\Omega$  pull-down resistor to

GND for output enable active low. See 3. "Ordering Information" on page 7.

### Table 2. CLK± Output Frequency Characteristics

| Parameter                        | Symbol         | Test Condition                            | Min | Тур  | Max  | Units |

|----------------------------------|----------------|-------------------------------------------|-----|------|------|-------|

| Nominal Frequency <sup>1,2</sup> | f <sub>O</sub> | LVPECL/LVDS/CML                           | 10  | —    | 810  | MHz   |

|                                  |                | CMOS                                      | 10  |      | 160  |       |

| Initial Accuracy                 | f <sub>i</sub> | Measured at +25 °C at time of<br>shipping | _   | ±1.5 | _    | ppm   |

| Total Stability                  |                | Note 3, second option code "D"            |     |      | ±20  | ppm   |

|                                  |                | Note 3, second option code "C"            |     | _    | ±30  | ppm   |

|                                  |                | Note 4, second option code "B"            |     | _    | ±50  | ppm   |

|                                  |                | Note 4, second option code "A"            |     |      | ±100 | ppm   |

| Temperature Stability            |                | second option code "D"                    |     |      | ±7   | ppm   |

|                                  |                | second option code "C"                    |     |      | ±20  | ppm   |

|                                  |                | second option code "B"                    | _   |      | ±25  | ppm   |

|                                  |                | second option code "A"                    |     | —    | ±50  | ppm   |

| Powerup Time <sup>5</sup>        | tosc           |                                           |     | _    | 10   | ms    |

#### Notes:

- 1. See Section 3. "Ordering Information" on page 7 for further details.

- 2. Specified at time of order by part number.

- 3. Includes initial accuracy, temperature, shock, vibration, power supply and load drift, and 10 years aging at 40 °C. See 3. "Ordering Information" on page 7.

- 4. Includes initial accuracy, temperature, shock, vibration, power supply and load drift, and 15 years aging at 70 °C. See 3. "Ordering Information" on page 7.

- 5. Time from powerup or tristate mode to  $f_{O}$ .

| Parameter                         | Symbol                         | Test Condition                                                                                                                  | Min                    | Тур                    | Max                    | Units           |

|-----------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-----------------|

| LVPECL Output Option <sup>1</sup> | Vo                             | mid-level                                                                                                                       | V <sub>DD</sub> – 1.42 | _                      | V <sub>DD</sub> – 1.25 | V               |

|                                   | V <sub>OD</sub>                | swing (diff)                                                                                                                    | 1.1                    | _                      | 1.9                    | V <sub>PP</sub> |

|                                   | V <sub>SE</sub>                | swing (single-ended)                                                                                                            | 0.55                   | _                      | 0.95                   | V <sub>PP</sub> |

| LVDS Output Option <sup>2</sup>   | V <sub>O</sub>                 | mid-level                                                                                                                       | 1.125                  | 1.20                   | 1.275                  | V               |

|                                   | V <sub>OD</sub>                | swing (diff)                                                                                                                    | 0.5                    | 0.7                    | 0.9                    | V <sub>PP</sub> |

|                                   | V                              | 2.5/3.3 V option mid-level                                                                                                      | —                      | V <sub>DD</sub> – 1.30 | —                      | V               |

| $\mathbf{O}$                      | Vo                             | 1.8 V option mid-level                                                                                                          | _                      | V <sub>DD</sub> - 0.36 |                        | V               |

| CML Output Option <sup>2</sup>    | V                              | 2.5/3.3 V option swing (diff)                                                                                                   | 1.10                   | 1.50                   | 1.90                   | M               |

|                                   | V <sub>OD</sub>                | 1.8 V option swing (diff)                                                                                                       | 0.35                   | 0.425                  | 0.50                   | V <sub>PP</sub> |

| CMOS Output Option <sup>3</sup>   | V <sub>OH</sub>                |                                                                                                                                 | 0.8 x V <sub>DD</sub>  | —                      | V <sub>DD</sub>        | V               |

|                                   | V <sub>OL</sub>                |                                                                                                                                 | —                      | —                      | 0.4                    | v               |

| Rise/Fall time (20/80%)           | t <sub>R,</sub> t <sub>F</sub> | LVPECL/LVDS/CML                                                                                                                 | —                      | _                      | 350                    | ps              |

|                                   |                                | CMOS with $C_L = 15 \text{ pF}$                                                                                                 |                        | 2                      |                        | ns              |

| Symmetry (duty cycle)             | SYM                            | LVPECL:         V <sub>DD</sub> - 1.3 V (diff)           LVDS:         1.25 V (diff)           CMOS:         V <sub>DD</sub> /2 | 45                     | _                      | 55                     | %               |

**1.** 50  $\Omega$  to V<sub>DD</sub> – 2.0 V. **2.** R<sub>term</sub> = 100  $\Omega$  (differential). **3.** C<sub>L</sub> = 15 pF. Sinking or sourcing 12 mA for V<sub>DD</sub> = 3.3 V, 6 mA for V<sub>DD</sub> = 2.5 V, 3 mA for V<sub>DD</sub> = 1.8 V.

#### Table 4. CLK± Output Phase Jitter

| Parameter                                                                                       | Symbol | Test Condition                                   | Min | Тур | Max | Units |

|-------------------------------------------------------------------------------------------------|--------|--------------------------------------------------|-----|-----|-----|-------|

| Phase Jitter (RMS) <sup>1</sup><br>for 50 MHz ≤ F <sub>OUT</sub> ≤ 810 MHz<br>(LVPECL/LVDS/CML) | фJ     | 12 kHz to 20 MHz                                 | _   | 0.5 | 1.0 | ps    |

| Phase Jitter (RMS) <sup>1</sup><br>(LVPECL/LVDS/CML)                                            | фј     | 12 kHz to 20 MHz,<br>155.52 MHz output frequency | _   | 0.4 | 0.7 | ps    |

| Phase Jitter (RMS) <sup>2</sup><br>for 50 MHz ≤ F <sub>OUT</sub> ≤ 160 MHz<br>(CMOS)            | фJ     | 12 kHz to 20 MHz                                 |     | 0.6 | 1.0 | ps    |

Notes:

**1.** Refer to AN256 for further information.

2. Single-ended CMOS output phase jitter measured using 33  $\Omega$  series termination into 50  $\Omega$  phase noise test equipment. 3.3 V supply voltage option only.

### Table 5. CLK± Output Period Jitter

| Parameter                           | Symbol           | Test Condition                   | Min         | Тур          | Max         | Units  |

|-------------------------------------|------------------|----------------------------------|-------------|--------------|-------------|--------|

| Period Jitter*                      | J <sub>PER</sub> | RMS                              | —           |              | 3           | ps     |

|                                     |                  | Peak-to-Peak                     |             |              | 35          |        |

| *Note: Any output mode, including C | CMOS, LVPI       | ECL, LVDS, CML. N = 1000 cycles. | Refer to AN | 279 for furt | her informa | ation. |

## Table 6. Environmental Compliance and Package Information

| Parameter                  | Conditions/Test Method   |

|----------------------------|--------------------------|

| Mechanical Shock           | MIL-STD-883, Method 2002 |

| Mechanical Vibration       | MIL-STD-883, Method 2007 |

| Solderability              | MIL-STD-883, Method 2003 |

| Gross and Fine Leak        | MIL-STD-883, Method 1014 |

| Resistance to Solder Heat  | MIL-STD-883, Method 2036 |

| Moisture Sensitivity Level | J-STD-020, MSL1          |

| Contact Pads               | Gold over Nickel         |

## **Table 7. Thermal Characteristics**

(Typical values  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V)

| Parameter                              | Symbol         | Test Condition | Min | Тур  | Max | Unit |

|----------------------------------------|----------------|----------------|-----|------|-----|------|

| Thermal Resistance Junction to Ambient | $\theta_{JA}$  | Still Air      | _   | 84.6 | _   | °C/W |

| Thermal Resistance Junction to Case    | $\theta_{JC}$  | Still Air      | _   | 38.8 | _   | °C/W |

| Ambient Temperature                    | T <sub>A</sub> |                | -40 | _    | 85  | °C   |

| Junction Temperature                   | Т <sub>Ј</sub> |                |     |      | 125 | °C   |

### Table 8. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                                                     | Symbol            | Rating                        | Units   |

|-------------------------------------------------------------------------------|-------------------|-------------------------------|---------|

| Maximum Operating Temperature                                                 | T <sub>AMAX</sub> | 85                            | °C      |

| Supply Voltage, 1.8 V Option                                                  | V <sub>DD</sub>   | -0.5 to +1.9                  | V       |

| Supply Voltage, 2.5/3.3 V Option                                              | V <sub>DD</sub>   | -0.5 to +3.8                  | V       |

| Input Voltage (any input pin)                                                 | VI                | -0.5 to V <sub>DD</sub> + 0.3 | V       |

| Storage Temperature                                                           | Τ <sub>S</sub>    | -55 to +125                   | °C      |

| ESD Sensitivity (HBM, per JESD22-A114)                                        | ESD               | 2500                          | V       |

| Soldering Temperature (Pb-free profile) <sup>2</sup>                          | T <sub>PEAK</sub> | 260                           | °C      |

| Soldering Temperature Time @ T <sub>PEAK</sub> (Pb-free profile) <sup>2</sup> | t <sub>P</sub>    | 20–40                         | seconds |

#### Notes:

1. Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation or specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

2. The device is compliant with JEDEC J-STD-020C. Refer to Si5xx Packaging FAQ available for download at www.silabs.com/VCXO for further information, including soldering profiles.

# Si590/591

# 2. Pin Descriptions

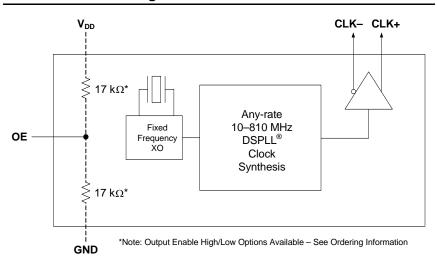

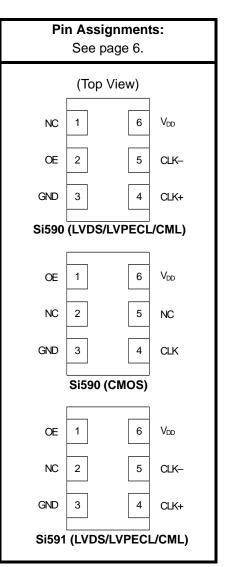

### Table 9. Pinout for Si590 Series

| Pin   | Symbol          | LVDS/LVPECL/CML Function                                                                                                         | CMOS Function                                            |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1     | OE*             | No connection<br>Make no external connection to this pin                                                                         | Output enable                                            |

| 2     | OE*             | Output enable                                                                                                                    | No connection<br>Make no external connection to this pin |

| 3     | GND             | Electrical and Case Ground                                                                                                       | Electrical and Case Ground                               |

| 4     | CLK+            | Oscillator Output                                                                                                                | Oscillator Output                                        |

| 5     | CLK-            | Complementary Output                                                                                                             | No connection<br>Make no external connection to this pin |

| 6     | V <sub>DD</sub> | Power Supply Voltage                                                                                                             | Power Supply Voltage                                     |

| *Note |                 | es an internal 17 k $\Omega$ pullup resistor to V <sub>DD</sub> for outputit enable active low. See 3. "Ordering Information" of |                                                          |

### Table 10. Pinout for Si591 Series

| Pin | Symbol                                                                                                        | LVDS/LVPECL/CML Function                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1   | OE*                                                                                                           | Output enable                                                                                                  |

| 2   | No connection<br>Make no external connection to this pin                                                      | No connection<br>Make no external connection to this pin                                                       |

| 3   | GND                                                                                                           | Electrical and Case Ground                                                                                     |

| 4   | CLK+                                                                                                          | Oscillator Output                                                                                              |

| 5   | CLK-                                                                                                          | Complementary output                                                                                           |

| 6   | V <sub>DD</sub>                                                                                               | Power Supply Voltage                                                                                           |

|     | DE pin includes an internal 17 k $\Omega$ pullup resistor<br>SND for output enable active low. See 3. "Orderi | r to $V_{DD}$ for output enable active high or a 17 k $\Omega$ pulldown resistor to ng Information" on page 7. |

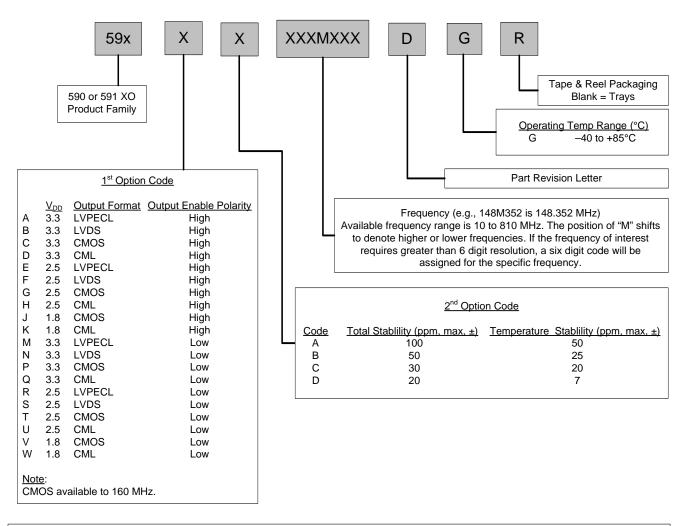

# 3. Ordering Information

The Si590/591 XO supports a variety of options including frequency, temperature stability, output format, and V<sub>DD</sub>. Specific device configurations are programmed into the Si590/591 at time of shipment. Configurations can be specified using the Part Number Configuration chart below. Silicon Laboratories provides a web browser-based part number configuration utility to simplify this process. Refer to www.silabs.com/VCXOPartNumber to access this tool and for further ordering instructions. The Si590 and Si591 XO series are supplied in an industry-standard, RoHS compliant, 6-pad,  $5 \times 7$  mm package. The Si591 Series supports an alternate OE pinout (pin #1) for LVPECL, LVDS, and CML output formats. See Tables 9 and 10 for the pinout differences between the Si590 and Si591 series.

Example P/N: 590BB148M352DGR is a 5 x 7 XO in a 6 pad package. The frequency is 148.352 MHz, with a 3.3 V supply, LVDS output, and Output Enable active high polarity. Overall stability is specified as  $\pm$ 50 ppm. The device is specified for -40 to +85 °C ambient temperature range operation and is shipped in tape and reel format.

#### Figure 1. Part Number Convention

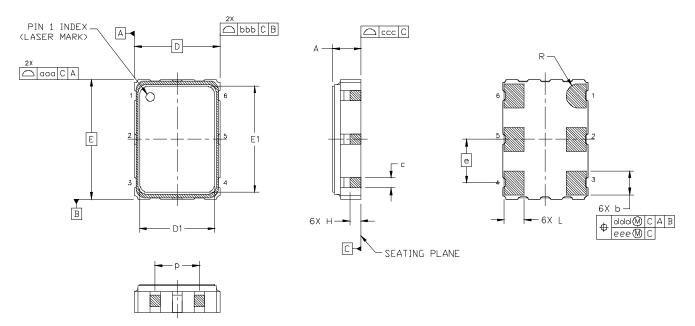

# 4. Outline Diagram and Suggested Pad Layout

Figure 2 illustrates the package details for the Si590/591. Table 11 lists the values for the dimensions shown in the illustration.

| Dimension | Min      | Nom      | Max  |  |  |  |

|-----------|----------|----------|------|--|--|--|

| A         | 1.50     | 1.65     | 1.80 |  |  |  |

| b         | 1.30     | 1.40     | 1.50 |  |  |  |

| С         | 0.50     | 0.60     | 0.70 |  |  |  |

| D         |          | 5.00 BSC |      |  |  |  |

| D1        | 4.30     | 4.40     | 4.50 |  |  |  |

| е         |          | 2.54 BSC |      |  |  |  |

| E         | 7.00 BSC |          |      |  |  |  |

| E1        | 6.10     | 6.20     | 6.30 |  |  |  |

| Н         | 0.55     | 0.65     | 0.75 |  |  |  |

| L         | 1.17     | 1.27     | 1.37 |  |  |  |

| р         | 1.80     | —        | 2.60 |  |  |  |

| R         |          | 0.70 REF |      |  |  |  |

| aaa       |          | 0.15     |      |  |  |  |

| bbb       |          | 0.15     |      |  |  |  |

| CCC       | 0.10     |          |      |  |  |  |

| ddd       |          | 0.10     |      |  |  |  |

| eee       |          | 0.50     |      |  |  |  |

### Table 11. Package Diagram Dimensions (mm)

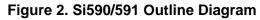

# 5. 6-Pin PCB Land Pattern

Figure 3 illustrates the 6-pin PCB land pattern for the Si590/591. Table 12 lists the values for the dimensions shown in the illustration.

Figure 3. Si590/591 PCB Land Pattern

| Dimension | Min      | Max  |

|-----------|----------|------|

| D2        | 5.08 REF |      |

| е         | 2.54 BSC |      |

| E2        | 4.15 REF |      |

| GD        | 0.84     | _    |

| GE        | 2.00     | _    |

| VD        | 8.20 REF |      |

| VE        | 7.30 REF |      |

| X         | 1.70 TYP |      |

| Y         | 2.15 REF |      |

| ZD        | _        | 6.78 |

| ZE        |          | 6.30 |

#### Table 12. PCB Land Pattern Dimensions (mm)

**1.** Dimensioning and tolerancing per the ANSI Y14.5M-1994 specification.

2. Land pattern design based on IPC-7351 guidelines.

3. All dimensions shown are at maximum material condition (MMC).

4. Controlling dimension is in millimeters (mm).

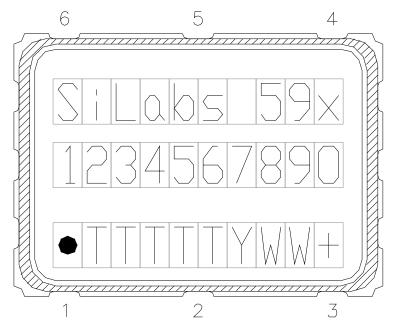

# 6. Si590/Si591 Top Marking

Figure 4 illustrates the mark specification for the Si590/Si591. Table 13 lists the line information.

Figure 4. Top Mark Specification

Table 13. Si59x Top Mark Description

| Line | Position     | Description                                                                                                                             |  |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | 1–10         | "SiLabs"+ Part Family Number, 59x (First 3 characters in part number where x indicates a 590 device and $x = 1$ indicates a 591 device) |  |

| 2    | 1–10         | Si590, Si591: Option1 + Option2 + Freq(7) + Temp<br>Si590/Si591 w/ 8-digit resolution: Option1 + Option2 + ConfigNum(6) + Temp          |  |

| 3    | Trace Code   |                                                                                                                                         |  |

|      | Position 1   | Pin 1 orientation mark (dot)                                                                                                            |  |

|      | Position 2   | Product Revision (D)                                                                                                                    |  |

|      | Position 3–6 | Tiny Trace Code (4 alphanumeric characters per assembly release instructions)                                                           |  |

|      | Position 7   | Year (least significant year digit), to be assigned by assembly site (ex: 2009 = 9)                                                     |  |

|      | Position 8–9 | Calendar Work Week number (1–53), to be assigned by assembly site                                                                       |  |

|      | Position 10  | "+" to indicate Pb-Free and RoHS-compliant                                                                                              |  |

# DOCUMENT CHANGE LIST

### **Revision 0.2 to Revision 0.25**

- Total Stability Maximum changed to ±30 in Table 2 on page 2.

- Total Stability Maximum changed to ±30 in Figure 1 on page 7.

### Revision 0.25 to Revision 0.3

- Updated Table 4 on page 3 by adding the 155.51 MHz "Phase Jitter (RMS) (LVPECL/LVDS/CML)" row.

- Updated and clarified Table 6 on page 4 to correct typos and include the "Moisture Sensitivity Level" and "Contact Pads" rows.

- Corrected BSC value in rows D and E in Table 11 on page 8.

### Revision 0.3 to Revision 0.4

Added ±7 ppm temperature stability ordering option in Table 4 on page 3 and Figure 1 on page 7.

### **Revision 0.4 to Revision 1.0**

- Updated 2.5 V/3.3 V and 1.8 V CML output level specifications in Table 3 on page 3.

- Updated Si590/591 devices to support frequencies up to 810 MHz for LVPECL, LVDS, and CML outputs.

- Separated 1.8 V, 2.5 V/3.3 V supply voltage. specifications for CML output in Table 3 on page 3.

- Updated Note 1 of Table 4 on page 3 to refer to AN256.

- Updated Table 4 on page 3.

- Updated phase jitter specification.

- Updated Table 6 on page 4 to include the "Moisture Sensitivity Level" and "Contact Pads" rows.

- Updated Figure 3 and Table 13 on page 10 to reflect specific marking information.

- Added Table 7, "Thermal Characteristics," on page 4.

- Rearranged sections to conform to new quality standard.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories, A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

### http://www.silabs.com