# AMD Embedded PCIe® ADD-IN BOARD **Datasheet** (ER93FLA/ER91FLA-xx)

Manufacturer P/N: ER93FLA-PI2(FH Fansink) Manufacturer P/N: ER93FLA-PI2(FH Fanless) Manufacturer P/N: ER93FLA-PI2(LP Fansink) Manufacturer P/N: ER93FLA-PI2(LP Fanless) Manufacturer P/N: ER93FLA-PI3(FH Fansink)

# **CONTENTS**

| 1. | Feature                                    |                           |    |  |  |

|----|--------------------------------------------|---------------------------|----|--|--|

| 2. | Functi                                     | Functional Overview4      |    |  |  |

|    | 2.1.                                       | Memory Interface          | 4  |  |  |

|    | 2.2.                                       | Acceleration Features     | 4  |  |  |

|    | 2.3.                                       | Avivo™ Display System     | 5  |  |  |

|    | 2.4.                                       | DVI/HDMI Features         | 5  |  |  |

|    | 2.5. DisplayPort Features                  |                           | 5  |  |  |

|    | 2.5.1 DisplaPort 1.1a Features 5           |                           |    |  |  |

|    | 2.5.2 D                                    | isplayPort 1.2 Features   | 6  |  |  |

|    | 2.6.                                       | CRT DAC                   | 6  |  |  |

|    | 2.7.                                       | Bus Support Features      | 7  |  |  |

| 3. | PIN As                                     | ssignment and Description | 8  |  |  |

| 4. | Power                                      | r Consumption             | 12 |  |  |

| 5. | Output configuration and Board Dimension13 |                           |    |  |  |

|    | 5.1.                                       | Output Configuration      | 13 |  |  |

|    | 5.2 Board Dimension14                      |                           |    |  |  |

| 6. | Thermal Mechanism                          |                           |    |  |  |

# 1. Feature

| Model Name                                          | ER93FLA                                                  | ER91FLA                                                  |

|-----------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|

| Graphics Processing Unit                            |                                                          |                                                          |

| Process Technology                                  | 40 nm                                                    | 40 nm                                                    |

| Graphics Engine Operating<br>Frequency (max)        | 600 MHz                                                  | 600 MHz                                                  |

| Form Factor                                         | ATX (168 x 69 mm)                                        | ATX (168 x 69 mm)                                        |

| GPU Interface                                       | PCI Express <sup>®</sup> 2.1 (X16)                       | PCI Express <sup>®</sup> 2.1 (X16)                       |

| Shader Processing Units                             | 6 SIMD engines x 80 processing<br>elements = 480 shaders | 2 SIMD engines x 80 processing<br>elements = 160 shaders |

| Floating Point Performance (single precision, peak) | 576 GFLOPs                                               | 192 GFLOPs                                               |

| DirectX <sup>®</sup> capability                     | DirectX <sup>®</sup> 11                                  | DirectX <sup>®</sup> 11                                  |

| Shader Model                                        | Shader Model 5.0                                         | Shader Model 5.0                                         |

| OpenGL                                              | OpenGL 4.1                                               | OpenGL 4.1                                               |

| OpenCL™ compliant                                   | AMD APP8, OpenCLTM 1.19,<br>DirectCompute 11             | AMD APP8, OpenCLTM 1.19,<br>DirectCompute 11             |

| Unified Video Decoder (UVD)                         | UVD3 for H.264, VC-1, MPEG-2, MPEG-4<br>part 2 decode    | UVD3 for H.264, VC-1, MPEG-2,<br>MPEG-4 part 2 decode    |

| Memory                                              |                                                          |                                                          |

| Operating Frequency (max)                           | 800 MHz / 3.2 Gbps                                       | 800 MHz / 3.2 Gbps                                       |

| Configuration, type                                 | 128-bit wide, 1 GB, GDDR5, 51.2 GB/s                     | 64-bit wide, 512 MB, GDDR5, 25.6<br>GB/s                 |

| Display Interfaces                                  |                                                          |                                                          |

| Single / Dual-Link DVI                              | Dual-Link DVI X1                                         | Dual-Link DVI X1                                         |

| CRT                                                 | CRT X1                                                   | CRT X1                                                   |

| HDMI 1.4                                            | HDMI X1                                                  | HDMI X1                                                  |

# 2. Functional Overview

#### 2.1. Memory Interface

AMD Radeon E6760 has four DRAM sequencers, E6469 has two DRAM sequencers. Each DRAM channel is 32-bit wide. Four/two 32 Mb × 32 GDDR5 memory chips are embedded on the ASIC for a total of 1G/512 MB Memory.

#### **2.2. Acceleration Features**

- Z Fully DirectX<sup>®</sup> 11 compliant, including full-speed 32-bit floating point per component operation:

- Z Shader Model 5.0 geometry and pixel support in a unified shader architecture.

- Z Support for OpenGL 4.1.

- Z Support for OpenCL<sup>tm</sup> 1.1

- Z Anti-aliasing filtering:

- ,, 2x/4x/8x/16x modes.

- ,, Multi-sample algorithm with gamma correction, programmable sample patterns, and centroid sampling.

- ,, Temporal anti-aliasing.

- ,, Adaptive anti-aliasing mode.

- ,, Lossless color compression (up to 8:1).

- Z Anisotropic filtering:

- ,, 2x/4x/8x/16x modes.

- ,, Up to 128-tap texture filtering.

- ,, Anisotropic biasing to allow trading quality for performance.

- ,, Improved quality mode due to improved subpixel precision and higher precision LOD computations.

- ,, Advanced texture compression (3Dc+<sup>™</sup>).

- ,, High quality 4:1 compression for normal and luminance maps.

- " Works with any single- or two-channel data format

- Z Up to 16k × 16k textures, including 128-bit/pixel texture are supported.

- Z Fully associative texture, color, and z-cache design.

- Z Hierarchical z- and stencil-buffers with early z-test.

- Z Fast z-buffer clear.

- Z Fast color-buffer clear.

## 2.3. Avivo<sup>™</sup> Display System

The AMD Avivo<sup>™</sup> display system supports VGA, VESA super VGA, and accelerator mode graphics display on six independent display controllers. The full features of the AMD Avivo display system are outlined in the following sections.

#### 2.4. DVI/HDMI Features

- Z Advanced DVI capability supporting 10-bit HDR (high dynamic range) output.

- Z Supports industry-standard CEA-861B video modes including 480p, 720p, 1080i, and 1080p. For a full list of currently supported modes, contact your local AMD support person.

- Z Maximum pixel rates for 24-bpp outputs are:

- ,, DVI—162 MP/s (megapixels per second) per link for 30-bpp dual-link; double for 24-bpp dual-link.

- ,, HDMI—148.5 MP/s.

- Z Fully compliant with the DVI electrical specification.

### **2.5. DisplayPort Features**

#### 2.5.1 DisplaPort 1.1a Features

- Z Supports all the mandatory features of the DisplayPort Version 1.1a Specification and the following optional features on all links:

- " 30-bit support.

- ,, YCbCr 444 up to 30-bpp and 422 up to 20-bpp support.

- ,, HDCP support.

- ,, DisplayPort extension for test-automation features, including test-pattern generation.

- " DisplayPort audio.

- Each DisplayPort link can support three options for the number of lanes and two options for link-data rate as follows:

- ,, Four, two, or one lane(s).

- ,, 2.7- or 1.62-GHz link-data rate per lane.

- Z Supports all video modes supported by the display controller that do not over subscribe the link bandwidth.

**Enabling an Intelligent Planet**

- ,, Examples of supported pixel-rate/resolution support for four lanes at 2.7- GHz link rate:

- Link bandwidth allows pixel clocks of up to 359 MP/s for 24 bpp or 287 MP/s for 30 bpp.

- 2560 × 1600 @ 60Hz, 24 bpp is supported.

- ,, Examples of supported pixel-rate/resolution support for two lanes at 2.7- GHz link rate:

- Link bandwidth allows pixel clocks of up to 179 MP/s for 24 bpp or 143 MP/s for 30 bpp.

- 1920 × 1200 @ 60Hz, 24 bpp is supported.

- ,, The following table shows the maximum pixel rates for four, two, or one lane(s) at 2.7-GHz link rate.

#### 2.5.2 DisplayPort 1.2 Features

- Z Each DisplayPort 1.2 link can transport up to six video streams; one from each display engine.

- Z Each DisplayPort link can support three options for the number of lanes and three options for link-data rate as follows:

- ,, Four, two, or one lane(s).

- ,, 5.4-, 2.7-, or 1.62-GHz link-data rate per lane.

- Z Supports all video modes supported by the display controller that do not oversubscribe the link bandwidth.

- ,, Examples of supported pixel-rate/resolution support for four lanes at 5.4- GHz link rate:

- Link bandwidth allows pixel clocks of up to 718 MP/s for 24 bpp or 574 MP/s for 30 bpp.

- 2560 × 2048 @ 60Hz, 30 bpp is supported.

- ,, Examples of supported pixel-rate/resolution support for two lanes at 5.4- GHz link rate:

- Link bandwidth allows pixel clocks of up to 359 MP/s for 24 bpp or 287 MP/s for 30 bpp.

- 2560 × 1600 @ 60Hz, 30 bpp is supported.

#### 2.6. CRT DAC

- Z One integrated triple 10-bit DAC with built-in reference circuit.

- Z Single RGB-CRT output.

- Z Maximum pixel frequency of 400 MHz.

- Z Individual power-down feature for each of the three guns.

## 2.7. Bus Support Features

- Z Fully compliant with the PCI Express<sup>®</sup> Base Specification Revision 2.1.

- Z Supports ×1, ×2, ×4, ×8, and ×16 lane widths.

- Z Supports 2.5 GT/s and 5.0 GT/s link-data rates.

# 3. PIN Assignment and Description

| Pin | Side B Connector       |                               | Side A Connector |                          |

|-----|------------------------|-------------------------------|------------------|--------------------------|

| #   | Name                   | Description                   | Name             | Description              |

| 1   | +12v                   | +12 volt power                | PRSNT#1          | Hot plug presence detect |

| 2   | +12v                   | +12 volt power                | +12v             | +12 volt power           |

| 3   | RSVD                   | Reserved                      | +12v             | +12 volt power           |

| 4   | GND                    | Ground                        | GND              | Ground                   |

| 5   | SMCLK                  | SMBus clock                   | JTAG2            | тск                      |

| 6   | SMDAT                  | SMBus data                    | JTAG3            | TDI                      |

| 7   | GND                    | Ground                        | JTAG4            | TDO                      |

| 8   | +3.3v                  | +3.3 volt power               | JTAG5            | TMS                      |

| 9   | JTAG1                  | +TRST#                        | +3.3v            | +3.3 volt power          |

| 10  | 3.3Vaux                | 3.3v volt power               | +3.3v            | +3.3 volt power          |

| 11  | WAKE#                  | Link Reactivation             | PWRGD            | Power Good               |

|     |                        | Mecha                         | nical Key        |                          |

| 12  | RSVD                   | Reserved                      | GND              | Ground                   |

| 13  | GND                    | Ground                        | REFCLK+          | Reference Clock          |

| 14  | HSOp(0)                | Transmitter Lane              | REFCLK-          | Differential pair        |

| 15  | HSOn(0)                | 0, Differential<br>pair       | GND              | Ground                   |

| 16  | GND                    | Ground                        | HSIp(0)          | Receiver Lane 0,         |

| 17  | PRSNT#2 Hotplug detect |                               | HSIn(0)          | Differential pair        |

| 18  | GND                    | Ground                        | GND              | Ground                   |

| 19  | HSOp(1)                | Transmitter Lane              | RSVD             | Reserved                 |

| 20  | HSOn(1)                | 1, Differential<br>On(1) pair |                  | Ground                   |

| 21  | GND                    | Ground                        | HSIp(1)          | Receiver Lane 1,         |

| 22  | GND                    | Ground                        | HSIn(1)          | Differential pair        |

| 23 | HSOp(2) | Transmitter Lane        | GND     | Ground            |

|----|---------|-------------------------|---------|-------------------|

| 24 | HSOn(2) | 2, Differential<br>pair | GND     | Ground            |

| 25 | GND     | Ground                  | HSIp(2) | Receiver Lane 2,  |

| 26 | GND     | Ground                  | HSIn(2) | Differential pair |

| 27 | HSOp(3) | Transmitter Lane        | GND     | Ground            |

| 28 | HSOn(3) | 3, Differential<br>pair | GND     | Ground            |

| 29 | GND     | Ground                  | HSIp(3) | Receiver Lane 3,  |

| 30 | RSVD    | Reserved                | HSIn(3) | Differential pair |

| 31 | PRSNT#2 | Hot plug detect         | GND     | Ground            |

| 32 | GND     | Ground                  | RSVD    | Reserved          |

| 33 | HSOp(4) | Transmitter Lane        | RSVD    | Reserved          |

| 34 | HSOn(4) | 4, Differential<br>pair | GND     | Ground            |

| 35 | GND     | Ground                  | HSIp(4) | Receiver Lane 4,  |

| 36 | GND     | Ground                  | HSIn(4) | Differential pair |

| 37 | HSOp(5) | Transmitter Lane        | GND     | Ground            |

| 38 | HSOn(5) | 5, Differential<br>pair | GND     | Ground            |

| 39 | GND     | Ground                  | HSIp(5) | Receiver Lane 5,  |

| 40 | GND     | Ground                  | HSIn(5) | Differential pair |

| 41 | HSOp(6) | Transmitter Lane        | GND     | Ground            |

| 42 | HSOn(6) | 6, Differential<br>pair | GND     | Ground            |

| 43 | GND     | Ground                  | HSIp(6) | Receiver Lane 6,  |

| 44 | GND     | Ground                  | HSIn(6) | Differential pair |

| 45 | HSOp(7) | Transmitter Lane        | GND     | Ground            |

| 46 | HSOn(7) | 7, Differential<br>pair | GND     | Ground            |

| 47 | GND     | Ground                  | HSIp(7) | Receiver Lane 7,  |

| 48 | PRSNT#2 | Hot plug detect         | HSIn(7) | Differential pair |

| 49 | GND      | Ground                   | GND      | Ground            |

|----|----------|--------------------------|----------|-------------------|

| 50 | HSOp(8)  | Transmitter Lane 8,      | RSVD     | Reserved          |

| 51 | HSOn(8)  | Differential pair        | GND      | Ground            |

| 52 | GND      | Ground                   | HSIp(8)  | Receiver Lane 8,  |

| 53 | GND      | Ground                   | HSIn(8)  | Differential pair |

| 54 | HSOp(9)  | Transmitter Lane 9,      | GND      | Ground            |

| 55 | HSOn(9)  | Differential pair        | GND      | Ground            |

| 56 | GND      | Ground                   | HSIp(9)  | Receiver Lane 9,  |

| 57 | GND      | Ground                   | HSIn(9)  | Differential pair |

| 58 | HSOp(10) | Transmitter Lane 10,     | GND      | Ground            |

| 59 | HSOn(10) | Differential pair        | GND      | Ground            |

| 60 | GND      | Ground                   | HSIp(10) | Receiver Lane 10, |

| 61 | GND      | Ground                   | HSIn(10) | Differential pair |

| 62 | HSOp(11) | Transmitter Lane 11,     | GND      | Ground            |

| 63 | HSOn(11) | Differential pair        | GND      | Ground            |

| 64 | GND      | Ground                   | HSIp(11) | Receiver Lane 11, |

| 65 | GND      | Ground                   | HSIn(11) | Differential pair |

| 66 | HSOp(12) | Transmitter Lane 12,     | GND      | Ground            |

| 67 | HSOn(12) | Differential pair        | GND      | Ground            |

| 68 | GND      | Ground                   | HSIp(12) | Receiver Lane 12, |

| 69 | GND      | Ground                   | HSIn(12) | Differential pair |

| 70 | HSOp(13) | Transmitter Lane 13,     | GND      | Ground            |

| 71 | HSOn(13) | Differential pair        | GND      | Ground            |

| 72 | GND      | Ground                   | HSIp(13) | Receiver Lane 13, |

| 73 | GND      | Ground                   | HSIn(13) | Differential pair |

| 74 | HSOp(14) | Transmitter Lane         | GND      | Ground            |

| 75 | HSOn(14) | 14, Differential<br>pair | GND      | Ground            |

| 76 | GND      | Ground                   | HSIp(14) | Receiver Lane 14, |

| 77 | GND      | Ground                     | HSIn(14) | Differential pair |

|----|----------|----------------------------|----------|-------------------|

| 78 | HSOp(15) | Transmitter Lane           | GND      | Ground            |

| 79 | HSOn(15) | 15, Differential<br>pair   | GND      | Ground            |

| 80 | GND      | Ground                     | HSIp(15) | Receiver Lane 15, |

| 81 | PRSNT#2  | Hot plug present<br>detect | HSIn(15) | Differential pair |

| 82 | RSVD#2   | Hot Plug Detect            | GND      | Ground            |

# 4. Power Consumption

#### z ER93FLA

| Application          | Total ASIC Power + DRAM Power (W) |

|----------------------|-----------------------------------|

| Static Windows - 65c | 6.32                              |

| Application         | Total ASIC Power + DRAM Power (W) |

|---------------------|-----------------------------------|

| 3D Mark Vantage FT6 | 26.34                             |

#### z ER91FLA

| Application          | Total ASIC Power + DRAM Power (W) |

|----------------------|-----------------------------------|

| Static Windows - 65c | 3.02                              |

| Application         | Total ASIC Power + DRAM Power (W) |

|---------------------|-----------------------------------|

| 3D Mark Vantage FT6 | 12.14                             |

# 5. Output configuration and Board Dimension

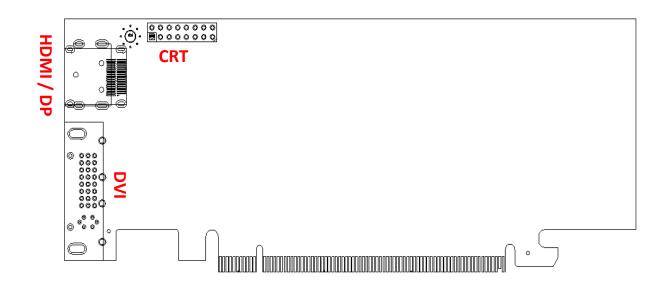

## 5.1. Output Configuration

z ER93FLA

z ER91FLA

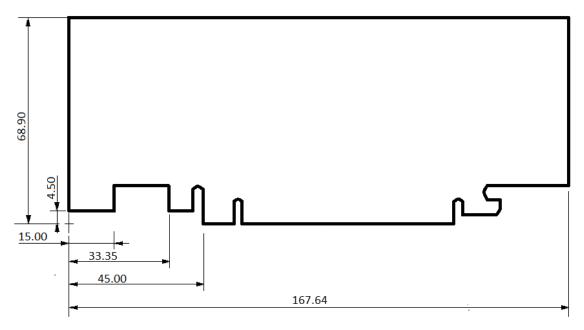

#### **5.2 Board Dimension**

# (Unit : mm)

Tolerances : +/\_ 0.13 mm

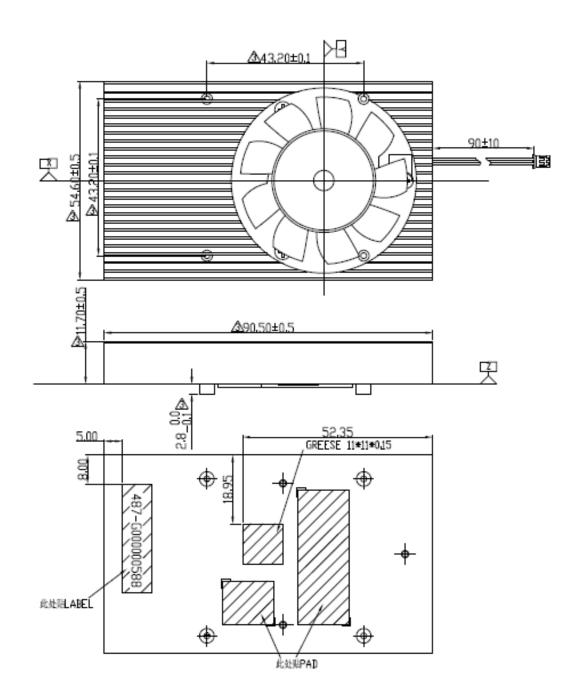

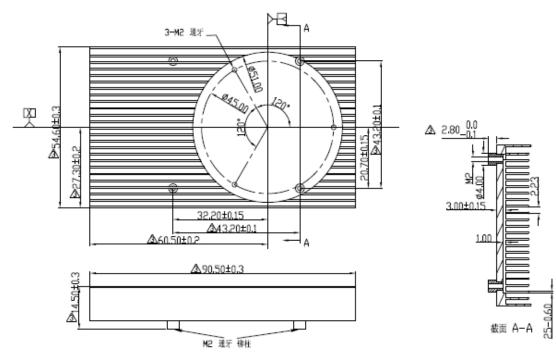

# 6. Thermal Mechanism

## (Unit : mm)

| Tolerances |          |  |

|------------|----------|--|

| 0-10       | +/- 0.1  |  |

| 10-50      | +/- 0.15 |  |

| 50-100     | +/- 0.2  |  |

| 100~       | +/- 0.25 |  |

# Change log or update history

| Rev. | Data      | History                  |

|------|-----------|--------------------------|

| 0.1  | 2012/6/21 | 1. 1 <sup>st</sup> Draft |

|      |           |                          |