#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <a href="http://www.nxp.com">http://www.nxp.com</a>, <a href="http://www.semiconductors.philips.com/">http://www.nxp.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>)

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use salesaddresses@nexperia.com (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

### **INTEGRATED CIRCUITS**

# DATA SHEET

For a complete data sheet, please also download:

- The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

- The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

# HEF4007UB gates Dual complementary pair and inverter

Product specification

File under Integrated Circuits, IC04

January 1995

## **Dual complementary pair and inverter**

HEF4007UB gates

#### **DESCRIPTION**

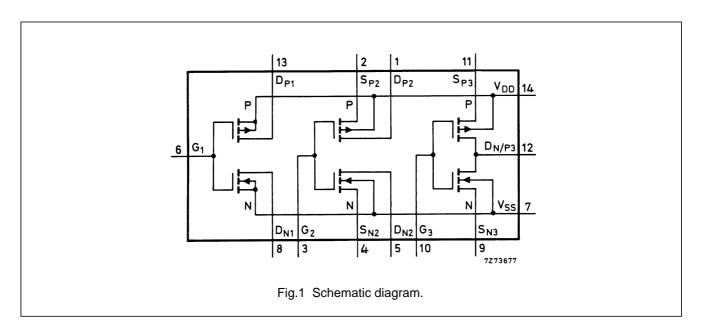

The HEF4007UB is a dual complementary pair and an inverter with access to each device. It has three n-channel and three p-channel enhancement mode MOS transistors.

PINNING

$S_{P2},\,S_{P3}$  source connections to 2nd and 3rd

p-channel transistors

$D_{P1},\,D_{P2}$  drain connections from the 1st and 2nd

p-channel transistors

$D_{N1},\,D_{N2}\quad \text{ drain connections from the 1st and 2nd}$

n-channel transistors

$S_{N2}$ ,  $S_{N3}$  source connections to the 2nd and 3rd

n-channel transistors

D<sub>N/P3</sub> common connection to the 3rd p-channel

and n-channel transistor drains

G<sub>1</sub> to G<sub>3</sub> gate connections to n-channel and

p-channel of the three transistor pairs

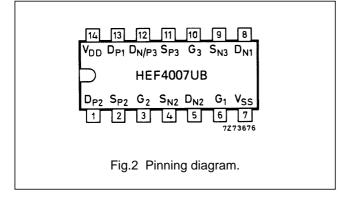

HEF4007UBP(N): 14-lead DIL; plastic

(SOT27-1)

HEF4007UBD(F): 14-lead DIL; ceramic (cerdip)

(SOT73)

HEF4007UBT(D): 14-lead SO; plastic

(SOT108-1)

(): Package Designator North America

#### FAMILY DATA, IDD LIMITS category GATES

See Family Specifications for  $V_{\text{IH}}/V_{\text{IL}}$  unbuffered stages

# Dual complementary pair and inverter

HEF4007UB gates

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                               | V <sub>DD</sub> | SYMBOL           | TYP. | MAX. |    | TYPICAL EXTRAPOLATION FORMULA       |

|-------------------------------|-----------------|------------------|------|------|----|-------------------------------------|

| Propagation delays            |                 |                  |      |      |    |                                     |

| $G_n \rightarrow D_N$ ; $D_P$ | 5               |                  | 40   | 80   | ns | 13 ns + (0,55 ns/pF) C <sub>L</sub> |

| HIGH to LOW                   | 10              | t <sub>PHL</sub> | 20   | 40   | ns | 9 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                               | 15              |                  | 15   | 30   | ns | 7 ns + (0,16 ns/pF) C <sub>L</sub>  |

|                               | 5               |                  | 40   | 75   | ns | 13 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH                   | 10              | t <sub>PLH</sub> | 20   | 40   | ns | 9 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                               | 15              |                  | 15   | 30   | ns | 7 ns + (0,16 ns/pF) C <sub>L</sub>  |

| Output transition times       | 5               |                  | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| HIGH to LOW                   | 10              | t <sub>THL</sub> | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                               | 15              |                  | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                               | 5               |                  | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| LOW to HIGH                   | 10              | t <sub>TLH</sub> | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                               | 15              |                  | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P (μW)                    |                                        |

|-----------------|----------------------|-----------------------------------------------|----------------------------------------|

| Dynamic power   | 5                    | 4500 $f_i + \sum (f_o C_L) \times V_{DD}^2$   | where                                  |

| dissipation per | 10                   | 20 000 $f_i + \sum (f_0 C_L) \times V_{DD}^2$ | f <sub>i</sub> = input freq. (MHz)     |

| package (P)     | 15                   | 50 000 $f_i + \sum (f_0 C_L) \times V_{DD}^2$ | f <sub>o</sub> = output freq. (MHz)    |

|                 |                      |                                               | C <sub>L</sub> = load capacitance (pF) |

|                 |                      |                                               | $\Sigma(f_0C_L)$ = sum of outputs      |

|                 |                      |                                               | V <sub>DD</sub> = supply voltage (V)   |

## Dual complementary pair and inverter

# HEF4007UB gates

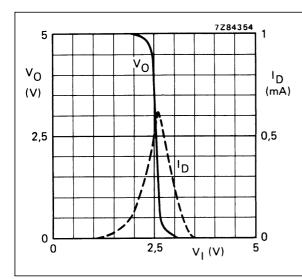

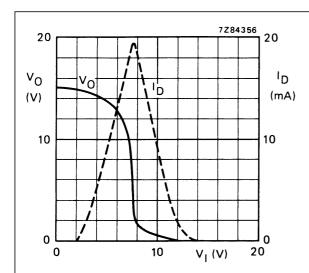

Fig.3 Typical drain current  $I_D$  and output voltage  $V_O$  as functions of input voltage;  $V_{DD} = 5 \text{ V}$ ;  $T_{amb} = 25 \text{ °C}$ .

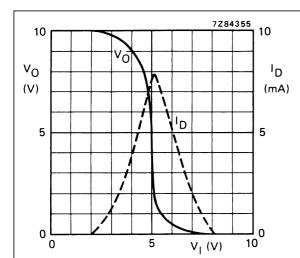

Fig.4 Typical drain current  $I_D$  and output voltage  $V_O$  as functions of input voltage;  $V_{DD}$  = 10 V;  $T_{amb}$  = 25 °C.

Fig.5 Typical drain current  $I_D$  and output voltage  $V_O$  as functions of input voltage;  $V_{DD}$  = 15 V;  $T_{amb}$  = 25 °C.

# Dual complementary pair and inverter

HEF4007UB gates

Product specification

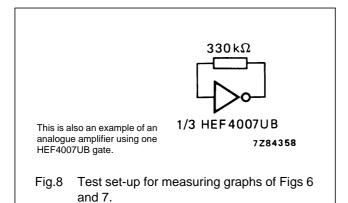

#### **APPLICATION INFORMATION**

Some examples of applications for the HEF4007UB are:

- · High input impedance amplifiers

- · Linear amplifiers

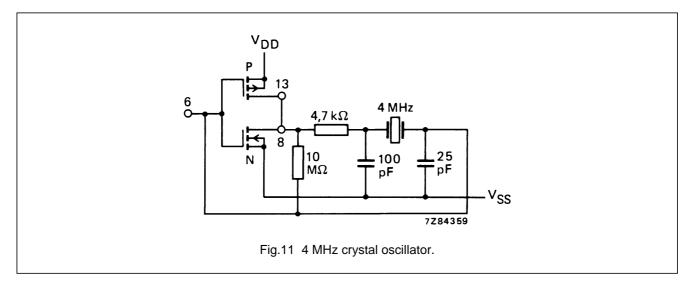

- · (Crystal) oscillators

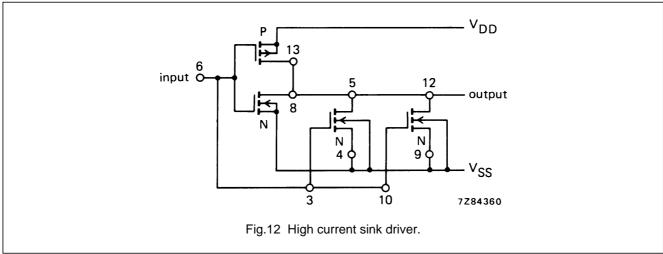

- High-current sink and source drivers

- High impedance buffers.

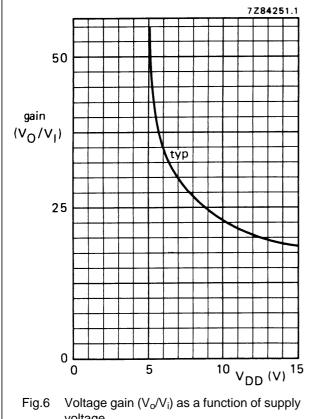

voltage.

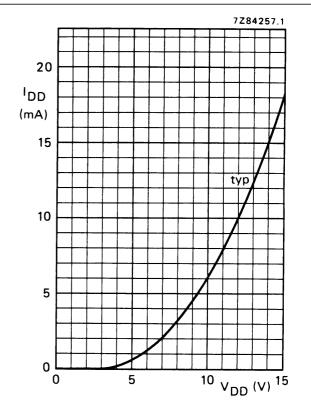

Supply current as a function of supply voltage.

## Dual complementary pair and inverter

# HEF4007UB gates

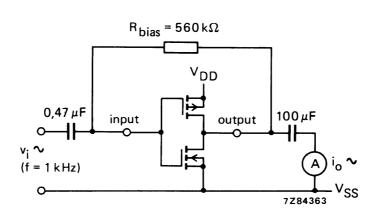

Fig.9 Test set-up for measuring forward transconductance  $g_{fs} = di_0/dv_i$  at  $v_0$  is constant (see also graph Fig.10).

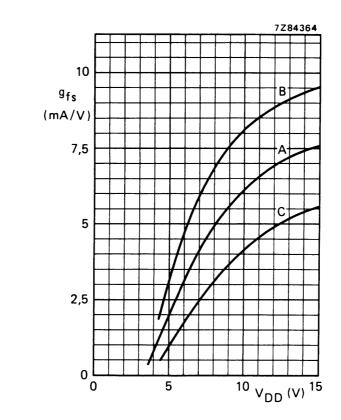

- A: average,

- B: average + 2 s

- C: average 2 s, in where 's' is the observed standard deviation.

Fig.10 Typical forward transconductance  $g_{fs}$  as a function of the supply voltage at  $T_{amb}$  = 25 °C.

# Dual complementary pair and inverter

HEF4007UB gates

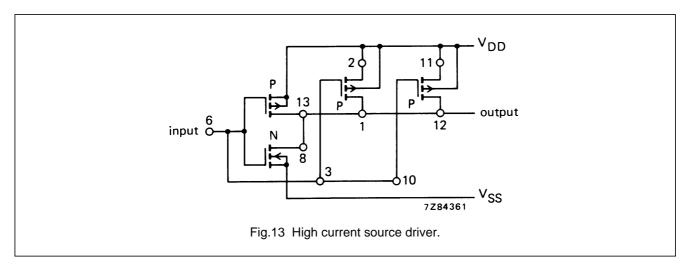

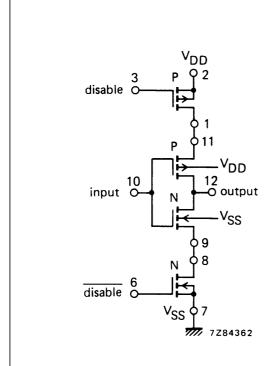

Figures 11 to 14 show some applications in which the HEF4007UB is used.

## Dual complementary pair and inverter

# HEF4007UB gates

Fig.14 High impedance buffer.

#### FUNCTION TABLE for Fig.14.

| INPUT | DISABLE | OUTPUT |

|-------|---------|--------|

| Н     | L       | L      |

| L     | L       | Н      |

| X     | Н       | open   |

#### **Notes**

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

#### **NOTE**

Rules for maintaining electrical isolation between transistors and monolithic substrate:

- Pin number 14 must be maintained at the most positive (or equally positive) potential with respect to any other pin of the HEF4007UB.

- Pin number 7 must be maintained at the most negative (or equally negative) potential with respect to any other pin of the HEF4007UB.

Violation of these rules will result in improper transistor operation and/or possible permanent damage to the HEF4007UB.