| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Applicable Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microsemi's™ PD64004AH is a 4-port,<br>mixed-signal, high-voltage Power over<br>Ethernet (PoE) Manager designed to<br>support IEEE 802.3af-2003 and 802.3at-<br>2009 PoE applications.<br>PD64004AH is used in Ethernet switches<br>(endspans) and midspans to enable next<br>generation network managers to share<br>power and data over the same cable. With<br>full digital control via a serial<br>communication interface and a minimum of<br>external components, the PD64004AH can<br>be placed in multi-port and highly<br>populated Ethernet switches. PD64004AH<br>integrates power, analog and logic<br>functions in a single 48-pin, QFN-PS<br>package allowing compact designs.<br>The PD64004AH detects IEEE 802.3af-<br>2003 compliant Powered Devices (PDs)<br>and 802.3at-2009 PDs which exceed<br>IEEE802.3af power levels, ensuring safe<br>power feeding and port disconnection.<br>The PD64004AH executes all real time<br>functions as specified in the IEEE 802.3af-<br>2003 standard and the IEEE802.3at-2009<br>standard including detection, 1-event<br>classification and port status monitoring. It<br>also executes system level activities such<br>as power management, and MIB support<br>for system management, and MIB support<br>for system management, the PD64004AH<br>is designed to detect and disable<br>disconnected ports, using both DC and AC<br>disconnection methods, as defined in IEEE<br>802.3af-2003 and IEEE802.3at-2009.<br>The PD64004AH, in conjunction with the<br>PD63000G or in Automatic mode, can be<br>configured to support 2-pair 802.3at-2009<br>(up to 600 mA.) and 2-pair standard "af"<br>power (up to 350mA) for full IEEE802.3af<br>compliant functionality. Further, in AF<br>mode the PD64004AH and PD63000G can<br>support 8-ports operation (when working<br>together, the units are in Enhanced mode).<br>Performance of the PD64004AH can be<br>fully evaluated using the PD-IM-7316AH<br>evaluation board.<br>IMPORTANT: For the most current data, consult<br>MICROSEMI's website: http://www.microsemi.com | <ul> <li>PoE Controller<br/>PD63000/G datasheet,<br/>Catalogue Number<br/>06-0008-058</li> <li>16 port evaluation<br/>board PD-IM-7316AH<br/>User Guide, Catalogue<br/>Number 06-0025-056</li> <li>Twelve-channel PoE<br/>manager PD64012GH<br/>datasheet, Catalogue<br/>Number 06-003-058</li> <li>AN-152, Designing 8-<br/>port PoE+ System<br/>Using PD64004AH,<br/>Catalogue Number<br/>06-0034-080</li> <li>AN-140, Layout Design<br/>Guidelines for PoE<br/>Systems, Catalogue<br/>Number 06-0012-080</li> <li>AN-161, Layout<br/>Guidelines for PoE<br/>Systems, Catalogue<br/>Number 06-0066-080.</li> <li>AN-170, Designing a<br/>16-port Enhanced PoE<br/>System, Catalogue<br/>Number 06-0042-080</li> </ul> | <ul> <li>IEEE 802.3af-2003 and<br/>802.3at-2009 compliant</li> <li>Up to 600 mA lport_max</li> <li>IETF Power Ethernet MIB<br/>(RFC 3621) compliant</li> <li>Single DC voltage input<br/>(44v-57v)</li> <li>Built in 3.3v regulator</li> <li>Low thermal dissipation<br/>(1 Ω sense resistor)</li> <li>Internal power-on reset</li> <li>Four ports</li> <li>Internal monitoring and<br/>protection</li> <li>Supports any PD64004AH<br/>and PD64012GH<br/>combination</li> <li>Can be cascaded for up to<br/>eight PoE managers</li> <li>I<sup>2</sup>C or UART<br/>communication to Host</li> <li>User friendly unique PoE<br/>communication protocol</li> <li>Direct register<br/>communication</li> <li>Continuous monitoring of<br/>individual ports</li> <li>Continuous system<br/>telemetries</li> <li>Parameters setting per port<br/>and per system</li> <li>Disabling of ports through<br/>hardware</li> <li>Enhanced power<br/>management algorithm</li> <li>Advanced power<br/>management; up to 32<br/>ports</li> <li>Pre-standard PD detection</li> <li>Detection of Cisco devices</li> <li>Port matrix</li> <li>Interrupt out</li> <li>Hardware system status pin</li> <li>LED support</li> <li>Emergency power<br/>management with up to<br/>eight power supplies</li> <li>Rmode for H/W<br/>configuration</li> <li>RoHS compliant</li> </ul> |

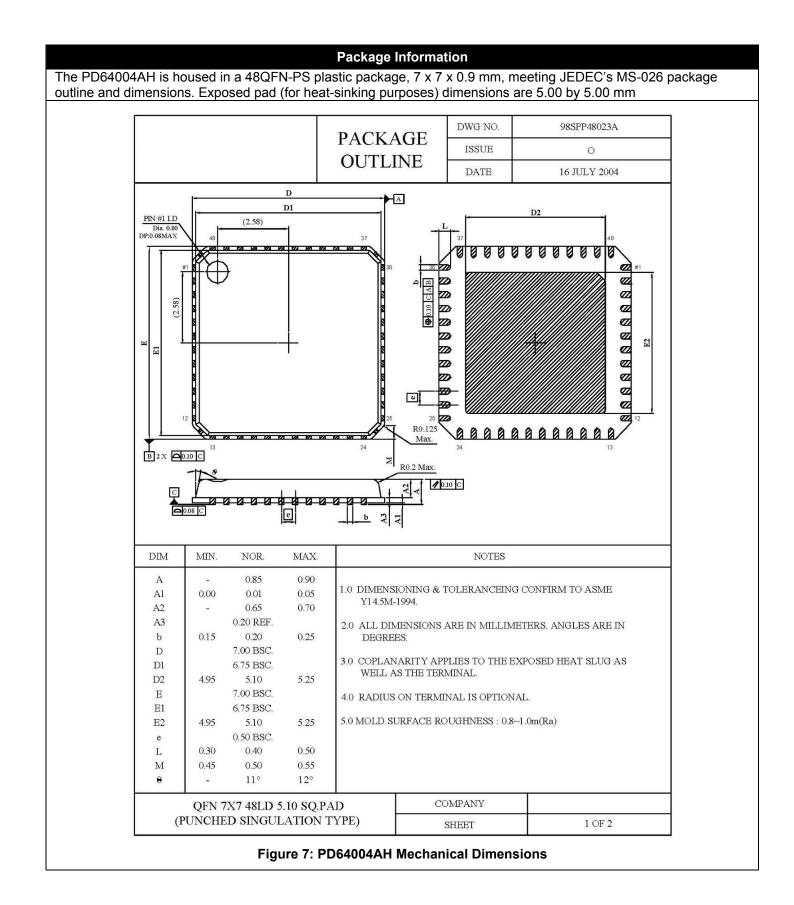

| PACKAGE ORDER INFO                                               |              |  |  |  |  |

|------------------------------------------------------------------|--------------|--|--|--|--|

| T <sub>A</sub> (°C)                                              | 48-Pin QFNPS |  |  |  |  |

|                                                                  |              |  |  |  |  |

| -40 to +70*/85** °C                                              | PD64004AH*** |  |  |  |  |

| * Temperature range for full 802.3at-2009 (up to 600 mA) load.   |              |  |  |  |  |

| ** Temperature range for full standard "af" (up to 350 mA) load. |              |  |  |  |  |

| *** 'H' Stands for 802.3at-2009                                  |              |  |  |  |  |

| Abso                                                                                                                                                                                          | lute Maximum Ratings                                                                                                  | Package Pin Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DGND, AGND, QGND,                                                                                                                                                                             | -0.3 to 80 VDC <sup>(1)</sup><br>SENSE_NEG0.3 to 0.3 VDC <sup>(2)</sup><br>0.3 to 80 VDC <sup>(1)</sup><br>_NEG       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PORT_SENSEx<br>VCC <sub>2p5</sub> , ADC <sub>2p5</sub><br>V <sub>PERI</sub><br>EXT_REG<br>I2CINI, ASICINI<br>MISO, MOSI, SCK,<br>SCL, SDA, CLK,<br>RESETN, CS0_N,<br>CS1_N<br>ESD (Human Body | 0.3 to 15 VDC<br>0.3 to 3 VDC<br>4 VDC<br>-0.3 to 6 VDC<br>-0.3 to 3 VDC<br>-0.3 to (VPERI + 0.3) VDC<br>-2 to 2 kV(3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Model)<br>Maximum junction<br>temperature $(T_{junc})$<br>Junction-ambient<br>thermal resistance<br>$(\theta_{JA})$                                                                           | -2 to 2 kV(3<br>+150° C<br>25 °C/W                                                                                    | VORT_RENGE         40         21         MISO           PORT_SENSE2         42         20         DISABLE_PORTS_N           PORT_SENSE2         42         42         20         DISABLE_PORTS_N           VPORT_NEG2         43 <part number="">         18         MOSI           PORT_SENSE1         44         <internal number="">         17         Reserved           PORT_SENSE1         45         <production info="">         16         PWRIN           SENSE_NEG         47          AGND         TEST_MODE</production></internal></part> |

| Junction-case<br>thermal resistance<br>$(\theta_{JC})$<br>Lead temperature<br>(soldering, 10 s)                                                                                               | 16° C/W<br>300° C                                                                                                     | veort_Post<br>veort_Post<br>veort_Post<br>veort_Post<br>veort_Post<br>Reserved<br>NMM<br>CP_UUT<br>REP_Port<br>Reserved<br>2P_IN                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>(2) Maximum value between g</li> <li>(3) ESD testing is performed in 100 pF, RZap = 1500 Ω)</li> <li>Stresses beyond those listed a</li> </ul>                                       | tage that can be applied for 1 minute maximum.                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

device reliability.

| Operating Conditions                                                                       |      |      |      |      |  |

|--------------------------------------------------------------------------------------------|------|------|------|------|--|

| PARAMETER                                                                                  | MIN. | NOM. | MAX. | UNIT |  |

| Operating temperature<br>at full 2-pair 802.3at-2009 load                                  | -40  |      | +70  | °C   |  |

| Operating temperature at full 2-pair<br>standard "af" power (up to 350mA) -40 +85 °C       |      |      |      |      |  |

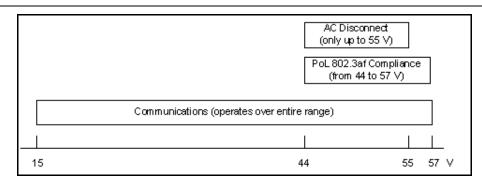

| Operational limitations (1)         15 to 44         44 to 55         55 to 57         VDC |      |      |      |      |  |

| 1. Operating functions depend on the input voltage, as shown in Figure 1.                  |      |      |      |      |  |

2. In order to get higher power drive at the PSE output ports, it is recommended to use operating voltage source Vmain > 50v

#### **Figure 1: Operational Ranges**

## **Electrical Characteristics**

| DC Characteristics for Digital Inputs and Outputs |                 |                    |               |           |                    |

|---------------------------------------------------|-----------------|--------------------|---------------|-----------|--------------------|

| PARAMETER                                         | SYMBOL          | MIN.               | MAX.          | UNIT      | REMARKS            |

| Pin Name                                          | DISABLE         | PORTS, SCI         |               |           |                    |

| Туре                                              | Schmitt Tr      | igger CMOS         | input, TTL le | evel with | internal pull-up   |

| High level input voltage                          | V <sub>IH</sub> | 2.0                |               | VDC       |                    |

| Low level input voltage                           | V <sub>IL</sub> |                    | 0.8           | VDC       |                    |

| Input voltage hysteresis                          |                 | 0.3                |               | VDC       |                    |

| Input high current                                | I <sub>IH</sub> | -1                 | +1            | μA        |                    |

| Input low current                                 | I <sub>IL</sub> | -1                 | +1            | μA        |                    |

| Pin Name                                          | SCL             |                    |               |           |                    |

| Туре                                              | Schmitt Tr      | igger CMOS         | input, TTL le | evel with | internal pull-up   |

| High level input voltage                          | VIH             | 2.0                |               | V         |                    |

| Low level input voltage                           | VIL             |                    | 0.8           | V         |                    |

| Pin Name                                          |                 | <u>O, CS0_N, C</u> |               |           |                    |

| Туре                                              | CMOS I/O,       | TTL level wit      | h no interna  |           | pull down resistor |

| High level input voltage                          | VIH             | 2.0                |               | VDC       |                    |

| Low level input voltage                           | VIL             |                    | 0.8           | VDC       |                    |

| Input voltage hysteresis                          |                 | 0.3                |               | VDC       |                    |

| Input high current                                | IIH             | -1                 | +1            | μA        |                    |

| Input low current                                 | IIL             | -1                 | +1            | μA        |                    |

| High level output voltage                         |                 | VPERI-0.4          |               | VDC       | lout = 2 mA        |

|                                                   |                 | VDC                |               |           |                    |

| DC Characteristics for Digital Inputs and Outputs |                                                              |      |      |      |             |

|---------------------------------------------------|--------------------------------------------------------------|------|------|------|-------------|

| PARAMETER                                         | SYMBOL                                                       | MIN. | MAX. | UNIT | REMARKS     |

| Low level output voltage                          |                                                              |      | 0.4  | VDC  | lout = 2 mA |

| Tri state output current                          |                                                              | -1   | +1   | μA   |             |

| Pin Name                                          | RESET_N,                                                     | SDA  |      |      |             |

| Туре                                              | CMOS open drain output with Schmitt Trigger input, TTL level |      |      |      |             |

| High level input voltage                          | VIH                                                          | 2.0  |      | VDC  |             |

| Low level output voltage                          | VOL                                                          |      | 0.4  | VDC  | lout = 6 mA |

| Low level input voltage                           | VIL                                                          |      | 0.8  | VDC  |             |

| Input voltage hysteresis                          |                                                              | 0.3  |      | VDC  |             |

| Off state output current                          |                                                              | -1   | +1   | μA   |             |

| Pin Name                                          | SDA_OUT, INT                                                 |      |      |      |             |

| Low Level output voltage                          |                                                              |      | 0.4  | VDC  | lout = 6 mA |

| Off state output current                          |                                                              | -1   | +1   | uA   |             |

| Electrical Characteristics for Analog I/O Pads |           |            |           |                                                                          |  |

|------------------------------------------------|-----------|------------|-----------|--------------------------------------------------------------------------|--|

| PARAMETER                                      | MIN.      | MAX.       | UNIT      | REMARKS                                                                  |  |

| Pin Name                                       | VPORT_P   | OSx        |           |                                                                          |  |

| Operating voltage                              | 44        | 62         | VDC       |                                                                          |  |

| Pin current consumption                        | -5        | +10        | μA        | Port driver off, Vport differential<br>measurement off, AC generator off |  |

| Pin Name                                       | VPORT_N   | EGx, REF_P | ORT_NE    | G                                                                        |  |

| Operating voltage                              | 44        | 62         | VDC       | Port driver off, Vport differential<br>measurement off, AC generator off |  |

| Pin current consumption                        | -10       | +10        | μA        |                                                                          |  |

| Pin Name                                       | PORT_SE   | NSEx       |           |                                                                          |  |

| Operating voltage                              | 0         | 1.48       | VDC       | With external 2 ohms (1%) to ground                                      |  |

| Internal current consumption                   |           | 20         | μA        |                                                                          |  |

| Pin Name                                       | VMAIN     |            |           |                                                                          |  |

| Operating voltage                              | 44        | 57         | VDC       |                                                                          |  |

| Vmain current consumption                      |           | 10         | mA        | Total on Vmain                                                           |  |

| Pin Name                                       | CP out    |            |           |                                                                          |  |

| Operating voltage                              | 44        | 68         | VDC       |                                                                          |  |

| Pin current consumption                        |           | 5          | mA        |                                                                          |  |

| Pin Name                                       | ADC2p5, V | CC2p5, VPE | ERI, EXT_ | REG                                                                      |  |

| ADC2p5 output voltage                          | 2.45      | 2.55       | VDC       |                                                                          |  |

| ADC2p5 internal current<br>consumption         |           | 6          | mA        | Recommended external cap. = 47 to 135<br>nF                              |  |

| VCC2p5 output voltage                          | 2.37      | 2.62       | V         | Recommended external cap. = 47 to 135<br>nF                              |  |

| VCC2p5 internal current consumption            |           | 5          | mA        |                                                                          |  |

| VPERI output voltage                           | 3.10      | 3.46       | VDC       | Recommended external cap. = 1 to 4.7 µF                                  |  |

| VPERI external current load                    |           | 6          | mA        | Without external NPN                                                     |  |

| EXT_REG output current                         |           | 30         | mA        | When using external NPN for VPERI                                        |  |

| Electrical Characteristics for Analog I/O Pads |                        |        |     |                                                  |  |  |

|------------------------------------------------|------------------------|--------|-----|--------------------------------------------------|--|--|

| PARAMETER                                      | MIN. MAX. UNIT REMARKS |        |     |                                                  |  |  |

| Pin Name                                       | ASICINI, I2            | CINI   |     |                                                  |  |  |

| Operating voltage                              | 0                      | ADC2p5 | VDC |                                                  |  |  |

| Current consumption                            | -1                     | +1     | μA  |                                                  |  |  |

| Pin Name                                       | I <sub>REF</sub>       |        |     |                                                  |  |  |

| Output voltage                                 | 1.21                   | 1.34   | VDC | With external 24.9 k $\Omega$ resistor to ground |  |  |

| Pin Name:                                      | PWRINI                 |        |     |                                                  |  |  |

| Operating voltage                              | 0                      | 100mV  | V   | From ADC2p5                                      |  |  |

| Internal current source                        | +1.5                   | 3      | uA  |                                                  |  |  |

## **Dynamic Characteristics**

The PD64004AH utilizes three programmable current level thresholds ( $I_{min}$ ,  $I_{cut}$ ,  $I_{lim}$ ) and two timers ( $T_{min}$ ,  $T_{cut}$ ). Loads that dissipate more than  $I_{cut}$  for longer than  $T_{cut}$  (OVL\_S to OVL) are classified as 'overloads' and are automatically shutdown. If output power is below  $I_{min}$  for more than  $T_{min}$  (UDL\_S to UDL) the PD is classified as 'no-load' and is shutdown.

Automatic recovery from overload and no-load conditions is attempted every  $T_{OVLREC}$  and  $T_{UDLREC}$  periods (typically 5 and 1 seconds, respectively). Output power is limited to  $I_{lim}$ , which is the maximum peak power allowed at the port.

| PARAMETER                                              |                     | CONDITIONS                                                                                                            | MIN. | TYP. | MAX.       | UNIT |

|--------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------------|------|

| Automatic recovery<br>from overload<br>shutdown        | T <sub>OVLREC</sub> | T <sub>OVLREC</sub> value, measured from port shutdown                                                                |      | 5    |            | s    |

| Automatic recovery<br>from no-load shutdown            | T <sub>UDLREC</sub> | value, measured from port shutdown                                                                                    |      | 1    |            | s    |

| Cutoff timers accuracy                                 |                     | Typical accuracy of Tcut                                                                                              |      | 3    |            | ms   |

| Inrush current                                         | I <sub>Inrsh</sub>  | AF mode – t = 50 ms, Cload =<br>180 uF max.<br>IEEE802.3at mode – t = 33 ms                                           |      | 654  | 450<br>692 | mA   |

| Output current operating range                         | Iport               | Continuous operation after startup period.                                                                            | 10   |      | 600        | mA   |

| Output power available, operating range                | P <sub>port</sub>   | Continuous operation after startup period, at port output.                                                            | 0.57 |      | 30         | W    |

| Off mode current                                       | I <sub>min1</sub>   | Must disconnect for t greater than TUVL                                                                               | 0    |      | 5          | mA   |

|                                                        | lmin2               | May or may not disconnect for t greater than TUVL                                                                     | 5    | 7.5  | 10         | mA   |

| PD power maintenance<br>request drop-out time<br>limit | T <sub>PMDO</sub>   | Buffer period to handle transitions<br>for both AF mode and IEEE802.3at<br>mode                                       | 300  |      | 400        | ms   |

| Over load current detection range                      | lcut                | AF mode - Time limited to TOVL                                                                                        | 350  |      | 400        | mA   |

|                                                        |                     | IEEE802.3at mode - Time limited to TOVL                                                                               | 600  |      | 615        |      |

| Over load time limit                                   | TOVL                | AF mode                                                                                                               | 50   |      | 75         | ms   |

|                                                        |                     | IEEE802.3at mode                                                                                                      |      | 33   |            |      |

| Turn on rise time                                      | T <sub>rise</sub>   | From 10% to 90% of $V_{port}$<br>(Specified for PD load consisting of 100 uF capacitor in parallel to 200 $\Omega$ ). | 15   |      |            | us   |

| Turn off time                                          | Toff                | From Vport to 2.8 VDC                                                                                                 |      |      | 500        | ms   |

### Thermal Data (Power Consumption)

The internal power consumption of a single PD64004AH from the DC input is based on:

Input voltage range: 44 to 57  $V_{\text{DC}}$  Input current: 7 mA maximum

$P_{MAIN} = V_{MAIN} \times I_{MAIN}$

Assuming the worst case, maximum power consumption is given by:

$P_{MAIN MAX} = 57 V_{DC} \times 7 mA = 0.4 W$

#### **Device Power Dissipation**

The PD64004AH integrates four power MOSFETs. Each MOSFET is characterized by:

- Drain-to-Source resistance,  $R_{DSON} = 0.3 \Omega$  typ; 0.5  $\Omega$  maximum

- Drain-Source current,  $I_{DS}$  = 600 mA max.

Hence, maximum power dissipation  $P_{MOSFET MAX}$  of a single PD64004AH device (for 4 MOSFETs) is given by:  $[(I_{DS})^2 \times R_{DSON\_MAX}] \times 4 = [(0.600 \text{ A})^2 \times 0.5 \Omega] \times 4$  = 0.73 W

Power dissipation of the internal charge pump,  $P_{CP}$  is 0.21 W.

Hence total power dissipation  $P_{TOTAL}$ , under maximum conditions is given by:  $P_{TOTAL} = P_{MAIN\_MAX} + P_{MOSFET\_MAX} + P_{CP}$

= 0.4 W + 0.73 W + 0.21 W

= 1.34 W

## **Protection Mechanism**

The PD64004AH includes an internal thermal protection feature, designed to protect the junction from overheating;

## **Configuration Pins**

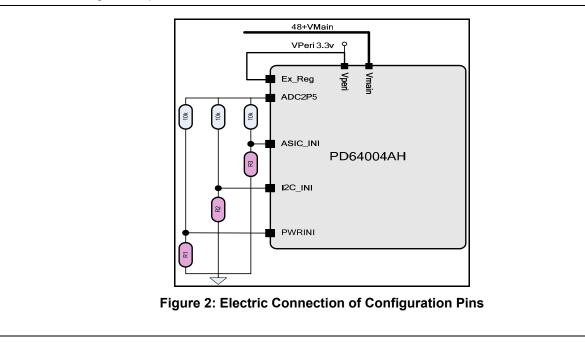

Three main configuration pins are utilized in the PD64004AH to reduce the need for communication (Figure 2).

#### Power\_ini

The power limit parameter is set by a resistor divider that actually sets the voltage at pin #16. There are 16 voltage levels that provide various power limit levels and guard-band levels as shown below:

| Mode Number | PWRINI Voltage<br>Level** | Power Limit<br>(W) | Guard Band<br>(W) |

|-------------|---------------------------|--------------------|-------------------|

| 1*          | 2.40 VDC to 2.50VDC       | 800                | 21                |

| 2           | 2.24VDC to 2.28VDC        | 22                 | 8                 |

| 3           | 2.08VDC to 2.13VDC        | 30                 | 8                 |

| 4           | 1.92VDC to 1.97VDC        | 35                 | 8                 |

| 5           | 1.76VDC to 1.82VDC        | 40                 | 8                 |

| 6           | 1.60VDC to 1.67VDC        | 45                 | 8                 |

| 7           | 1.44VDC to 1.52VDC        | 50                 | 10                |

| 8           | 1.28VDC to 1.36VDC        | 55                 | 10                |

| 9           | 1.13VDC to 1.21VDC        | 60                 | 10                |

| 10          | 0.97VDC to 1.06VDC        | 65                 | 10                |

| 11          | 0.81VDC to 0.90VDC        | 70                 | 10                |

| 12          | 0.65VDC to 0.75VDC        | 80                 | 13                |

| 13          | 0.49VDC to 0.60VDC        | 90                 | 13                |

| 14          | 0.33VDC to 0.44VDC        | 100                | 13                |

| 15          | 0.16VDC to 0.29VDC        | 110                | 13                |

| 16          | 0.00VDC to 0.14VDC        | 800                | 21                |

\* This mode should be set for applications that have a 2 Ω Rsense only. All other modes are for 1 Ω Rsense applications.

\*\*The above voltage values are calculated assuming that the ADC2p5 voltage is 2.5 VDC with accuracy of ±2%.

# ASIC\_INI

PoE Manager's configuration is performed via the ASIC\_INI pin, as shown below. The ASIC\_INI signal is converted into a 10-bit register (A/D). Once a hard reset pulse is detected, the data is latched into an internal mode register.

| Mode Name                                      | ASIC_INI Voltage Level |

|------------------------------------------------|------------------------|

| 802.3at-2009 mode (including standard AF mode) | 0.33v to 0.60v         |

## **Pinout Description**

|                | Funct     | ional Pin Description                            |

|----------------|-----------|--------------------------------------------------|

| Name           | Pin #     | Description                                      |

| VPORT POS0     | 1.        | Port 0 positive voltage feeding                  |

| VPORT POS1     | 2.        | Port 1 positive voltage feeding                  |

| VPORT POS2     | 3.        | Port 2 positive voltage feeding                  |

| VPORT POS3     | 4.        | Port 3 positive voltage feeding                  |

| Reserved       | 4.<br>5.  | Not connected                                    |

| Reserved       | 6.        | Not connected                                    |

| Reserved       | 7.        | Not connected                                    |

| VMAIN          | 8.        | Main voltage supply                              |

| CP IN          | 9.        | Charge pump input, Vmain                         |

| CP OUT         | 9.<br>10. | Charge pump output pulse                         |

| REF PORT NEG   | 10.       | Port negative reference                          |

| Reserved       | 11.       | Not connected                                    |

| TEST MODE      | 12.       |                                                  |

| AGND           | 13.       | Test mode pin – connect to AGND<br>Analog ground |

| Reserved       | 14.       | Not connected                                    |

| PWRINI         | 15.       | Preset power limit values                        |

| Reserved       | 16.       |                                                  |

|                |           | Not connected                                    |

| MOSI<br>DGND   | 18.       | SPI bus, master data out/slave in                |

| -              | 19.       | Digital ground                                   |

| DISABLE_PORTS_ | 20.       | Disable all ports power – active low             |

| MISO           | 21.       | SPI bus, master data in/slave out                |

| CS0_N          | 22.       | SPI bus, chip select 0                           |

| SDA_OUT        | 23.       | Third pin in I <sup>2</sup> C protocol           |

| CS1_N          | 24.       | SPI bus, chip select 1                           |

| SCK            | 25.       | SPI bus, serial clock I/O                        |

| SCL            | 26.       | I <sup>2</sup> C bus, serial clock Input         |

| SDA            | 27.       | I <sup>2</sup> C bus, open drain                 |

| RESET_N        | 28.       | Active Low Reset I/O                             |

| IREF           | 29.       | Current reference                                |

| ASICINI        | 30.       | Analog input for ASIC initialization             |

| VCC2p5         | 31.       | Internal 2.5v supply (do not use!)               |

| I2CINI         | 32.       | Analog input for I <sup>2</sup> C initialization |

| QGND           | 33.       | Quiet analog ground                              |

| ADC2p5         | 34.       | ADC reference (do not use!)                      |

| EXT_REG        | 35.       | External regulation                              |

| VPERI          | 36.       | Regulated 3.3v power source                      |

| INT            | 37.       | Interrupt, open drain                            |

| Reserved       | 38.       | Not connected                                    |

| AGND           | 39.       | Analog ground                                    |

| VPORT_NEG3     | 40.       | Port 3 negative voltage feeding                  |

| PORT_SENSE3    | 41.       | Channel current monitoring                       |

| PORT_SENSE2    | 42.       | Channel current monitoring                       |

| VPORT_NEG2     | 43.       | Port 2 negative voltage feeding                  |

| PORT_SENSE1    | 44.       | Channel current monitoring                       |

| VPORT_NEG1     | 45.       | Port 1 negative voltage feeding                  |

| PORT_SENSE0    | 46.       | Channel current monitoring                       |

| SENSE_NEG      | 47.       | Port sense reference                             |

| VPORT_NEG0     | 48.       | Port 0 negative voltage feeding                  |

#### Interrupt State - Machine

The interrupt state-machine obviates the need for communication between the host CPU and the PD64004AH. When a PoE event occurs, the interrupt pin level drops to 'low', thus the host CPU is notified. Then the host CPU requests information related to the event.

This method differs from the polling method, where the Host controller prompts all PoE Managers cyclically in order to receive information related to a PoE event.

When an event occurs, the type of event is entered into the main interrupt register which is the first register to be read by the Host after receiving an interrupt. There are two main event types.

The first event is a system event and the second is a port event. When a port event occurs, the host CPU should read another register to ascertain which port caused that event.

Port event registers are individually cleared right after reading them (clear on read).

If desired, one or more registers can be masked so as to avoid receiving non-desired interrupts by the Host. The following are the main events supported by the interrupt:

- Port power switched on

- Port power switched off due to:

- Port disable

- Overload, short condition or over temperature

- AC disconnect or DC disconnect

- Power management algorithm

- Port was started up

- AF detection completed successfully

- AF classification routine was completed. Asserted at the end of classification cycle.

- Vmain out-of-range

- Temperature out-of-range

## **Block Diagram**

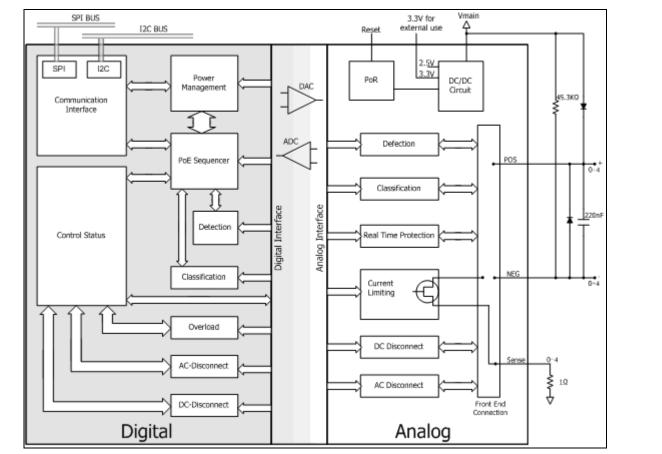

The PD64004AH PoE Manager complies with all the IEEE standard 802.3af-2003 detection requirements. PD64004AH is built around two major sections (Figure 3):

- A common digital section that serves all four channels

- Four separate identical channels for driving ports

Figure 3: Internal Block Diagram

## **Communication Interface**

The PD64004AH incorporates two communication interfaces. The first interface is an SPI bus which connects the PD63000G PoE Controller to the PD64004AHs. The second interface is an I<sup>2</sup>C used to communicate with the Host. Both interfaces transmit the contents of the internal registers between the PD64004AH logic and the PoE Controller.

#### Power Management

Receives data from the PoE sequencer and determines which port is to be connected and which port is to be disconnected, in accordance with the system's total power. This block is active in the **Master chip only**!

## **Control Status**

Several macros control the port enable function and others control the port disconnect function.

- Port enable: Resistor Line Detection, Classification.

- Port disable: AC Disconnect, DC Disconnect and Overload Logic.

These macros are connected to the Channel RT Control Status circuitry. Based on the inputs from these macros, the Channel RT controller starts the shutdown process or the recovery process.

This is performed in accordance with the pre-programmed parameters for different time windows.

| PoE Sequencer                                                                                                                                                                                                                                                                                                                                                                       | AC Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Current Limit                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The PoE Sequencer is the core of<br>the Digital section; it includes an<br>internal state machine that controls<br>the macros (described below) and<br>transfers the data from those macros.                                                                                                                                                                                        | The system applies a sinusoidal<br>signal to the positive port terminal.<br>The voltage developed on the port<br>terminals is proportional to the load<br>value. If the load is high, the AC<br>component riding on the port<br>terminals is low. If the load is low, the<br>AC component is high. A dedicated<br>circuit measures the AC component<br>level and compares it with a<br>pre-defined value stored in a register.<br>Based on the comparison's results,<br>the system determines whether to<br>disable a port or not. | This circuit continuously monitors<br>the current of powered ports and<br>limits the current to a specific value<br>in cases where an over load occurs.<br>If the current exceeds a specific<br>level, the system starts measuring<br>the elapsed time. If this time period<br>is greater than a preset threshold,<br>the port is disconnected. |

| Detection                                                                                                                                                                                                                                                                                                                                                                           | DC Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power on Reset (POR)                                                                                                                                                                                                                                                                                                                            |

| The PoE Controller or the PoE<br>sequencer generates a request to<br>apply separate voltage levels to the<br>output port. A measurement circuit<br>monitors the difference between the<br>various levels.<br>Voltage differences are compared<br>with values stored in the registers. By<br>comparing these values, the system<br>can determine whether to enable a<br>port or not. | This block senses when the port<br>current drops below 7.5 mA. If this is<br>the case, a flag is 'raised' and timers<br>in the Channel RT Controller start<br>counting. The Channel RT Controller<br>acts in accordance with pre-<br>programmed thresholds limits and<br>time windows, prior to initiating a<br>disconnect status for that port. The<br>circuitry takes into account PDs that<br>modulate their current consumption,<br>disconnecting them only if necessary.                                                      | The POR Monitors the internal DC<br>levels; if these voltages drop below<br>specific thresholds, a Reset signal<br>is generated and the PD64004AHs<br>are reset via the RESET_N pin.                                                                                                                                                            |

| Classification                                                                                                                                                                                                                                                                                                                                                                      | DC/DC Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Real Time Protection                                                                                                                                                                                                                                                                                                                            |

| Upon request from the PoE<br>Controller or from the PoE<br>sequencer, the state machine applies<br>a regulated 18 VDC to the port<br>output.<br>The current is measured by<br>comparing the real current flow with a<br>number of preset thresholds; in this<br>manner the class is verified.                                                                                       | This circuit produces 2.5V and 3.3V, derived from the Vmain main supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | This circuitry performs all real time<br>measurements and sends the<br>results to the logic circuitry in order<br>to determine whether to disconnect<br>a port or not.                                                                                                                                                                          |

| Overload                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                 |

| This block senses when the port<br>current exceeds the maximum<br>current level as specified in the IEEE-<br>802.3af standard, and disconnects<br>the port if required.                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                 |

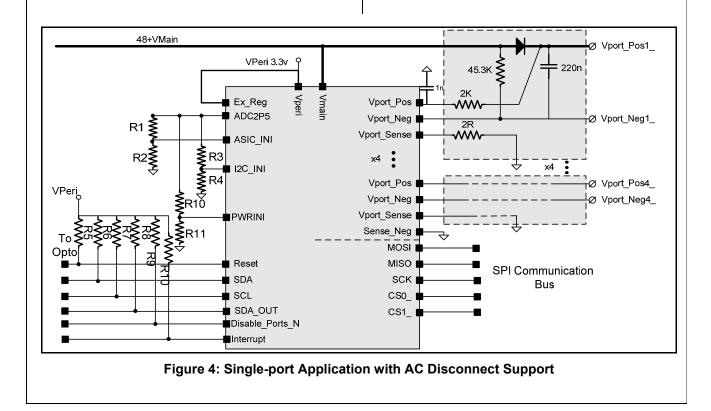

## **Application Information**

The PD64004AH can be integrated into a number of applications such as Ethernet switches, routers, Midspans, and more. Examples of such applications are described below:

- Integrated directly into a switch: Facilitates entire PoE concept, by including the IC(s) on the main switch's PCB.

- **Daughter board add-on:** Which the IC is integrated into a small PoE dedicated PCB, mounted on top of the switch's main PCB.

- **Midspans**: Stand alone devices, installed between the Ethernet switch and PDs (Powered Devices) such as telephone, camera, wireless LAN, etc.).

These Midspans include the PD64004AH IC as a PoE control element, designed to inject power over the communication lines.

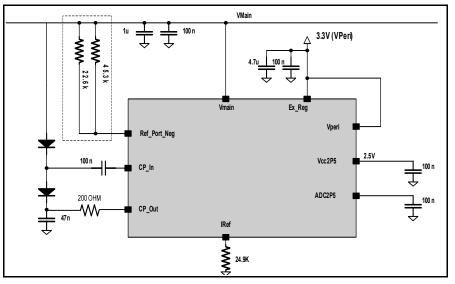

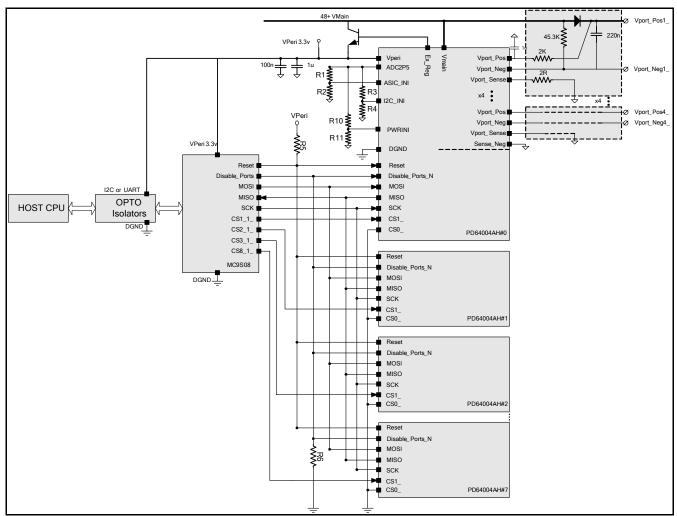

Figure 4 through Figure 6 provide detailed schematic diagrams for various applications of the PD64004AH.

Figure 5: Typical Power Filtering

Figure 6: Typical Application

| Feature                                   | Description                                                                         |  |

|-------------------------------------------|-------------------------------------------------------------------------------------|--|

| IEEE 802.3af-2003                         | The PD64004AH meets all IEEE-802.3af-2003 standard requirements including:          |  |

| Compliant                                 | Multi-point resistor detection                                                      |  |

|                                           | <ul> <li>PD 1-event classification function</li> </ul>                              |  |

|                                           | AC disconnection and DC disconnection functions                                     |  |

|                                           | Supports back-off feature for Midspan implementation                                |  |

| 802.3at-2009 Compliant                    | Enables detection and powering of 802.3at-2009 Compliant PDs via the two pair       |  |

|                                           | for pre-standard PDs.                                                               |  |

| IETF Power Ethernet                       | The PD64004AH meets all IETF power Ethernet MIB (RFC 3621) requirements             |  |

| MIB (RFC 3621)                            | including port enable/disable, port priority, classification, error counters and    |  |

| Compliant                                 | system/port power consumption.                                                      |  |

| Single DC Voltage Input                   | The PD64004AH requires a single DC voltage input: 44V to 57V. No additional         |  |

|                                           | voltage inputs (for example 3.3V/5V) are required to operate the PoE system.        |  |

| Built-In 3.3 Regulator                    | The PD64004AH, with few additional components can provide 3.3V source (up           |  |

| _                                         | to 30mA) for other peripherals such as a PoE Controller and opto-couplers.          |  |

| Low thermal                               | The PD64004AH has a very low thermal dissipation. It has an exposed pad that        |  |

| dissipation (1 $\Omega$ sense             | keeps the PoE Manager at a low temperature. The Rsense in PD64004AH                 |  |

| resistor)                                 | applications is only 1 $\Omega$ which keeps the peripheral components at a low      |  |

| •                                         | temperature as well.                                                                |  |

| Internal Power-on                         | The power-on reset circuitry monitors the internal voltage regulators (2.5V, Vperi  |  |

| Reset                                     | 3.3V and 10V). If one of these voltages drops below a pre-defined level, the        |  |

|                                           | PD64004AH is reset until all voltages rise above the proper levels again.           |  |

| Supports 4 Port PoE                       | The PD64004AH has high port density (4 ports) integrated into a single device,      |  |

| implementations                           | thus saving PCB space, reducing PoE system cost and simplifying the circuit         |  |

| Internal Power FET Per                    | design.<br>Four power FETs are integrated into a single PD64004AH to save PCB space |  |

| Port                                      | and simplify the circuit design. The exposed pad under the 48 QFN package           |  |

| FOIL                                      | dissipates the heat from the PD64004AH to the PCB.                                  |  |

| Thermal                                   | The PD64004AH integrates internal thermal protection features designed to           |  |

| Monitoring/Protection                     | protect the junction from overheating; Three types of temperature sensors are       |  |

|                                           | integrated on PD64004AH; two are utilized for protection and one is utilized for    |  |

|                                           | monitoring.                                                                         |  |

| Support any                               | PD64004AH can also be used with the PD64004AH, 4-Port PSE Manager, to               |  |

| PD64004AH and                             | implement more than 12 ports. Multiple PD64012GHs and PD64004AHs can be             |  |

| PD64012GH                                 | used simultaneously. This flexibility provides multiple port options, from 12 to 96 |  |

| Combination                               | ports, with minimizing costs and optimizing PCB space. In this implementation,      |  |

|                                           | either the PD64012GH or the PD64004AH can be configured as master or                |  |

|                                           | slave.                                                                              |  |

| Cascade up to Eight                       | Up to eight PD64004AHs can be cascaded to implement multiport PoE system            |  |

| PoE Managers                              | to a maximum of 96 ports.                                                           |  |

| I2C or UART<br>Communication to Host      | Enables I <sup>2</sup> C communication or UART Communication between the host CPU   |  |

|                                           | and the PoE controller for continuous monitoring and for port parameter setting.    |  |

| User Friendly Unique<br>PoE Communication | A unique 'Host CPU' - 'PoE Controller' communication protocol optimizes PoE         |  |

| Protocol                                  | continuous monitoring and simplifies PoE parameter setting.                         |  |

| Direct Register                           | The host CPU communicates with the PD64004AH PoE manager by writing and             |  |

| Communication                             | reading to/from its registers directly.                                             |  |

| Continuous Monitoring                     | The host CPU can receive on-line information per port such as:                      |  |

| of Individual Ports                       | <ul> <li>Port current and power measurement</li> </ul>                              |  |

|                                           | <ul> <li>Port class</li> </ul>                                                      |  |

|                                           | <ul> <li>Port status (on, off, overload, and short)</li> </ul>                      |  |

|                                           | <ul> <li>Port matrix, interrupt events, etc.</li> </ul>                             |  |

|                                           | • For main, interrupt events, etc.                                                  |  |

| Feature                          | Description                                                                                                                                                        |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Continuous System                | On-line system telemetries for the host CPU including:                                                                                                             |  |

| Telemetries                      | Voltage measurement                                                                                                                                                |  |

|                                  | Total system power consumption                                                                                                                                     |  |

|                                  | System and ICs status                                                                                                                                              |  |

| Parameters Setting per           | Configurable parameters via the host CPU including:                                                                                                                |  |

| Port and Per System              | Port priority                                                                                                                                                      |  |

|                                  | <ul> <li>Power management parameters (power limit, Guard band level,</li> </ul>                                                                                    |  |

|                                  | PM mode)                                                                                                                                                           |  |

|                                  | <ul> <li>Forced power and disable power per port</li> </ul>                                                                                                        |  |

|                                  | AC/DC disconnection method                                                                                                                                         |  |

|                                  | <ul> <li>LEDs parameters, port matrix, PoE Controller interrupt-out</li> </ul>                                                                                     |  |

|                                  | masks, flags, etc.                                                                                                                                                 |  |

| Disabling of Ports               | The PD64004AH features a dedicated pin (Disable_Ports) enabling an                                                                                                 |  |

| Through Hardware                 | immediate disconnection of all ports. It is controlled by the host CPU. All ports are disconnected when voltage level on this pin is low. This is the quickest way |  |

|                                  | to turn-off all ports.                                                                                                                                             |  |

| Enhanced Power                   | The system supports the following power management modes: Class mode,                                                                                              |  |

| Management Algorithm             | Allocation mode, Dynamic mode and Auto-PM mode, which combine all three                                                                                            |  |

| 6 6                              | modes. The power management feature is a continuous real-time algorithm                                                                                            |  |

|                                  | designed to prevent power consumption beyond a predefined limit.                                                                                                   |  |

|                                  | Disconnection and connection of ports is performed, as specified, in the power                                                                                     |  |

|                                  | management mode.                                                                                                                                                   |  |

| Advanced Power                   | Additional flags improve the power management algorithm and provide the host                                                                                       |  |

| Management for up to<br>96 Ports | with more flexibility when configuring the system.                                                                                                                 |  |

| Pre-Standard PD                  |                                                                                                                                                                    |  |

| Detection                        | Enables detection and powering of pre-standard PDs.                                                                                                                |  |

| Detection of Cisco               | Enables detection and powering of all Cisco devices including pre-standard                                                                                         |  |

| Devices                          | terminals.                                                                                                                                                         |  |

| Port Matrix                      | Allows the layout designer to connect the physical ports to the logical ports when                                                                                 |  |

|                                  | desired.                                                                                                                                                           |  |

| Interrupt - Out                  | Reduces communication overhead of the host CPU.                                                                                                                    |  |

|                                  | Whenever a PoE event (masked by the host CPU) occurs; the PoE Controller                                                                                           |  |

| Hardware System                  | sends an interrupt to signal the PoE event.<br>An optional hardware signal between the PoE Controller and the host CPU,                                            |  |

| Status Pin                       | provides the host CPU with a warning that a major failure (for example Vmain                                                                                       |  |

|                                  | out of range) has occurred.                                                                                                                                        |  |

| LED Support                      | Direct SPI interface to an external LED Stream circuitry. It enables the designer                                                                                  |  |

|                                  | to implement a simple LED circuit without any software code.                                                                                                       |  |

| Emergency Power                  | For systems comprising more than a single power supply, a fast port                                                                                                |  |

| Management                       | disconnection mechanism is activated in case one of the power supplies fails, to                                                                                   |  |

|                                  | maintain operation and prevent collapse of other power supplies. Up to eight                                                                                       |  |

| Dmode 11/M                       | power supplies are supported.                                                                                                                                      |  |

| Rmode – H/W<br>configuration     | H/W pin on the PoE Controller allows hardware configuration of the following                                                                                       |  |

| comguration                      | parameters:                                                                                                                                                        |  |

|                                  | <ul> <li>Power management mode</li> <li>AC or DC disconnect</li> </ul>                                                                                             |  |

|                                  | All ports ON or OFF                                                                                                                                                |  |

|                                  | <ul> <li>IEEE 802.3af detection or IEEE 802.3af &amp; pre-standard</li> </ul>                                                                                      |  |

|                                  | detection                                                                                                                                                          |  |

|                                  |                                                                                                                                                                    |  |

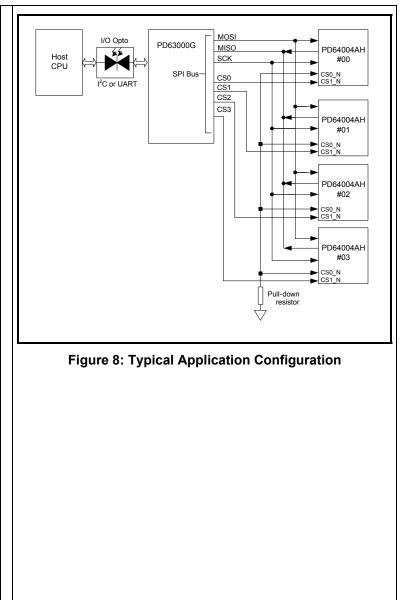

## System Description

PD64004AHs communicate with the PD63000G, PoE Controller (dedicated controller for PoE tasks), via a Serial Parallel Interface (SPI) bus. In this mode, all PD64004AHs are directly connected to the PD63000G via the SPI bus in slave mode. The switch host CPU communicates with the PD63000G via an isolated I<sup>2</sup>C or UART bus.

Figure 8 illustrates a typical application configuration.

The PD63000G controller is configured by the host CPU to initialize and control the PD64004AHs to support 802.3at-2009 PDs and/or IEEE802.3af standard PDs. The PD63000G is designed to perform enhanced sequential start-up mechanism and enhanced power management, maintaining temperature and stress levels within the specification.

#### 802.3at-2009

When configured for 802.3at-2009, each PD64004AH can support up to 600 mA per port (30 watts at PSE output @ 50v) on all the four ports. Under this configuration, if the PD is classified as Class #4, up to 600 mA is supported. If the PD is classified as Class #0, Class #1, Class #2 or Class #3, then standard power up to 350 mA is supported. Hence when configured for IEEE802.3at-2009 both 802.3at-2009 PDs and "af" PDs are supported depending on the class information.

### Standard "af" Power

When configured for standard "af" power, each PD64004AH can support up to 350 mA per port (15.4 watt at PSE output @ 44v) on all the four ports.